关于一段verilong代码的疑惑,希望各位大侠帮忙解答,谢谢!

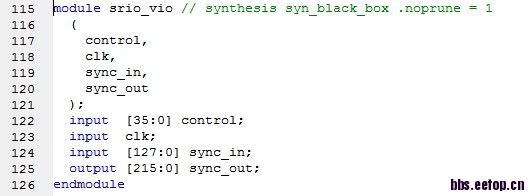

control,

clk,

sync_in,

sync_out

);

input [35:0] control;

input clk;

input [127:0] sync_in;

output [215:0] sync_out;

endmodule

这是rapidIO IPcore产生的文件中的一部分代码,这个module是在其中一个文件中声明的,模块里面没有任何的具体操作,而且这个文件中同时声明了很多个这样只有输入、输出定义没有具体操作的module,像这样的module放在一个文件里可以吗?而且就单独的一个module来说没有具体操作,对其例化有什么具体的意义,是不是只是产生了一个输出变变量?

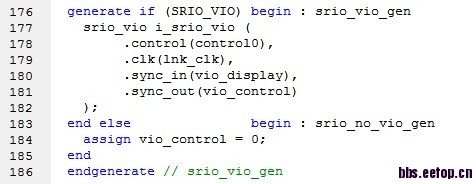

在另外一个文件中的generate语句中就例化了上面的module,我看不懂这是什么意思,而且在下面还有代码将vio_control的值赋给了其他的变量,这样做有意义吗?

generate if (SRIO_VIO) begin : srio_vio_gen

srio_vio i_srio_vio (

.control(control0),

.clk(lnk_clk),

.sync_in(vio_display),

.sync_out(vio_control)

);

end else begin : srio_no_vio_gen

assign vio_control = 0;

end

endgenerate

人家为了保护没把代码给你吧……

真正做到芯片里时肯定有功能的个人理解应该是一个内部设计的core,应该基于版权的考虑,故在程序库内部只用模块的名字进行了映射

哦,这样啊,明白了,我以为可以例化一个空的module呢,谢谢了!

综合的时候,可以看到里面的电路吗?

比较有道理! 学习了!

回复benny46:

这是一个xilinx 内rapidIO的core里example的一个文件的一部分,我综合所有的文件可以得到电路,我也认为一个空的module是不可以例化的,你怎么看呢?这是个黑盒,不是空模块,只是里面的电路不给你看...

black box,xilinx的话,综合时候有ngc文件就可以综合出电路来了。

这是一个虚拟的输入输出口,按照那个文档在板上测回还可以用到,如果直接用于数据的传输则不需要,我最近也在测这个,有些问题也想请教你。主要是FPGA是发起者那个部分没有调通。我的QQ是 304150939

能留下你的吗?我在用v5的板子,用的是SRIO V5.6协议,我看到UG503上说可以环回测试验证,然后我就在外部用SMA将TX和RX对接,但是这样,port_initialed拉低状态,难道不可以只使用一个核进行环回测试吗?必须要再加一个核吗?另外example_design的VIO必须给信号,才能实现读写吗,不是直接固化在程序里面吗?

另外,可以再一片FPGA上使用两个SRIO核吗,我的方案是想加一个CPS1848芯片,作为stwich交换,通信。但是在一个工程里例化两个SRIO时,时钟错误一直有,就是约束文件一个文件里面可以有多个module,但是不推荐这样做。因为如果文件多的话不方便对模块管理。

还有就是generate语句是根据你的SRIO_VIO参数值判断是否例化一个VIO控制模块。这写输出的值都是可以通过chipscope来控制的。希望能帮到LZ