请教一个USB2.0接口到FPGA的通信问题

复位的时候给32'hffff_ffff ,先写入一个固定数据,例如32'h01020304,看看pc机读到是什么数据。

你好 我没有用到复位引脚 会不会是由这个原因导致的? 我主要参考官网的AN61345这个例子来的

你好 我没有用到复位引脚 会不会是由这个原因导致的? 我主要参考官网的AN61345这个例子来的,另外我爸EP6设置为四重缓存,可是在使用CyConsole读数据是却可以一直读取数据,而不是读取完四次就失败了,usb芯片的FLAGA,FLAGB,FLAGD这些可以反应usb的EP6区空满状态的引脚在做板子的时候没有给到fpga,所以fpga无法获取EP6的空满状态,所以fpga一直把slwr信号拉低,让他一直写数据,说以我考虑会不会由于一直这样写数据导致EP6满了,所以会出现全是零的状况,你看会是这个原因吗?

从下面这段用户手册的说明来看,并没有说不需要接Reset Pin哦。你稍微研究一下这个芯片是否有自动power on reset,否则这可能是个问题。

另一个可能的问题,你可以研究一下里面的sram,你FPGA一直驱动,是否会导致内部sram一直在write,如果是个单口ram的话,是否导致无法read。另外,你说的溢出导致ram里面内容为0,这不大可能的。

2.9.1 Reset Pin

The input pin, RESET#, resets the FX2LP when asserted.

Thispin has hysteresis and is active LOW. When a crystal is

used withthe CY7C680xxA the reset period must enable

stabilization ofthe crystal and the PLL. This reset period

must be approximately

5 ms after VCC reaches 3.0V. If the crystal input pin is

driven bya clock signal the internal PLL stabilizes in 200 ms

after VCC hasreached 3.0V.[3]

Figure 2-2 on page 8

shows a power on reset condition and areset applied

during operation. A power on reset is defined asthe time

reset that is asserted while power is being applied to thecircuit.

A powered reset is when the FX2LP powered on andoperating

and the RESET# pin is asserted.

Cypress provides an application note which describes

andrecommends power on reset implementation. For

moreinformation about reset implementation for the FX2

family ofproducts visit http://www.cypress.com.

好的谢谢你的回复,今天忘记看帖子了,我再来检查一遍

小编 还是不行 我有一个计数器,当写入1024个数据时,把写信号拉高,但是使用cyconsole看到的却是1024个00啊,也就是说数据写进去了,但是为什么全是零啊

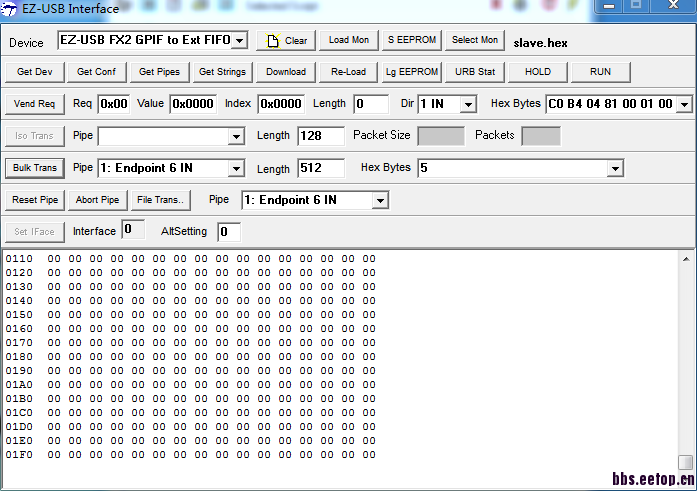

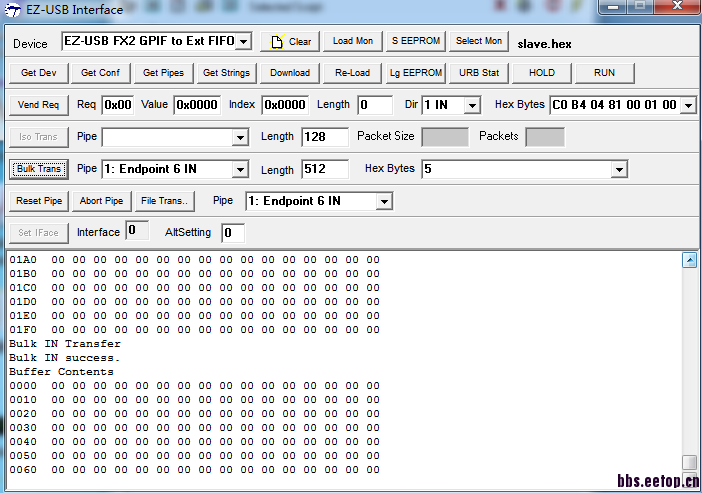

你好,我做了一个计数器,让他写进512个字节的数据时,停止写入,此时我读到的却是512个00,可是我检测那十六跟数据线FD[15:0]上面有数据跳动,现在这样会是什么原因?

如果是一块memory在usb的芯片里,你写入的数据如果不是全0,读出来的是全0.表示写入是失败的。你可以检查一下write 接口信号的时序,看是否满足usb芯片的时序要求。

usb的时序要求只有2~48mhz之间,另外在同步模式中,usb的时序要和FPGA的时序有180度的相移,就这两个要求吧另外在同步slave fifo中,write信号有效后,在usb信号的每个上升沿将数据写入usb吧 是这样吧?