virtex6 lm605开发板高速lvds时钟产生?

1、DCM+BUFG+ODDR+LVDS

2、DCM+BUFG+OSERDES+LVDS

看不到波形额

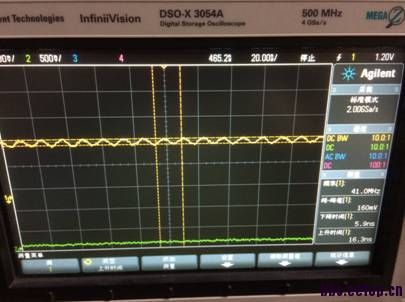

谢谢您的回复,看波形好像是上升沿比较缓慢,大概16ns,这样的话就不可能产生80M的时钟啊?

波形不是很清楚,看上去似乎被转接板反灌了一个直流电压。你只是需要一个80M的时钟么?我目前的ML605的FPGA工程的时候基本都是跑100M左右,运行很正常,就是采用晶振的66M时钟,经过PLL分频生成的。

谢谢回复,这个信号是没有接AD板,直接测GPIO得到的,采用的是LVDS接口标准,所以存在一个月1.2V的工模电压,并表示AD引起的。你说的100M是直接管脚上输出的,还是内部的信号,内部100M时钟是很容易实现的,我是希望跟AD对接,所以需要FPGA管脚输出给AD芯片。非常感谢您的回复!

波形是对的,我使用200MHz的晶振给AD,然后AD输出数据参考时钟给FPGA,也是200MHz的LVDS信号,也是DCM+BUFG+ODDR+LVDS的结构,没有问题(不过我使用的是ZYNQ7),可以尝试一下加一下时钟约束,加了约束比没加约束效果好很多。

#NET "adc_clk_in" TNM_NET = adc_clk_in;

#TIMESPEC TS_adc_clk_in = PERIOD "adc_clk_in" 5 ns HIGH 50%;

#NET "adc_clk_in" CLOCK_DEDICATED_ROUTE = TRUE;

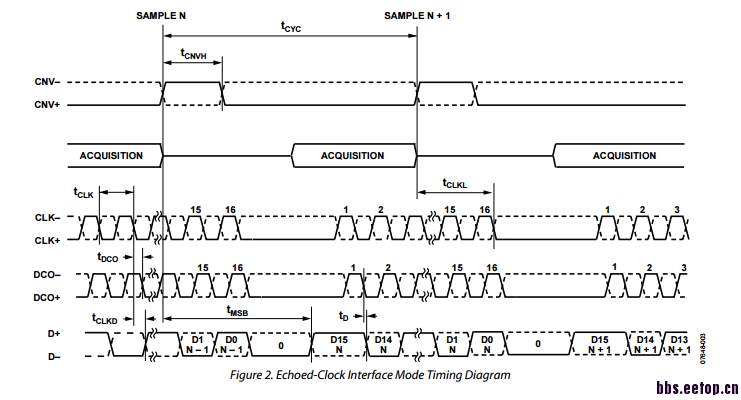

谢谢您的回复,请问您使用的也是AD7626吗?这个芯片有两种模式:Echoed-clock和self-clocked,测试时我使用的是self-clocked模式,采用FPGA直接给AD提供时钟,这样是不是对那个时钟要求更高?我等下去试试Echoed-clock模式,您说的时序约束我是加在DCM之前的,用它产生的时钟应该会自动添加时序约束的,还有您是直接用晶振给AD提供200M时钟的,但是我看手册上说,不需要时钟时时钟线要保持在0,这个没关系吗?

又去试了下,发现真的没加时序约束,加了之后FPGA管脚输出明显信号明显变好啦,谢谢了,但是接上AD板之后又变差了,这个应该是信号完整性的问题啦,在去调调看,非常感谢!

没有用过AD7626,我使用的是TI公司的ADC10DV200,10位,最大200MSPS的并行接口AD,另外使用了一个DAC3162,12位,最大500MSPS的DA,现在DA最大能以400MSPS的速度工作。使用的是xilinx提供的IP模块SELECTIO,你的AD最好使用IP模块serial_IO,一般XILIINX它都能综合得很好(我的里面也没有加什么复杂的处理,没加什么时序约束)。我觉得时钟的话谁给是没有关系的,只要符合要求就行,上面的DA的数据时钟就是由FPGA给的,所以我觉得你的用法是没有关系。至于信号完整性问题的话,那就比较麻烦了,如果是反射的问题,看看能否在末端加上匹配电阻试试。如果是差分线对长度的问题,那估计要改版了。我现在的设计方法是使用载板+FMC子板的方式,中间的走线其实也很长(大概3000mil),也没有做端接,但差分对线长,以及差分对总线的线长做了严格的等长。我也没有做过很多的高速应用,以上只是我的应用之谈,也不知道对你有没有用处。

恩,了解了,做了约束之后可以产生80M时钟啦,现在主要是数据线进过开发板之后,信号质量就变差啦,我现在正在找找开发板上其他的管脚用于捕获数据,开发板上留的GPIO真心不多,而且一般都用来做一些指示用的,估计板子上的走线没怎么处理,谢谢您的回复,我再去试试。

刚把数据线管教换了位子,现在用示波器查看,信号质量应该可以了,但是出现一个问题,当时钟频率为80M时,采集数据错位,20M时,数据正确,怀疑是AD板到lm605开发板走线较长,导致输出给AD板的时钟以及AD输出给FPGA的数据存在延迟,导致内部采集提前,请问这个有什么方法解决吗?offset约束好像也不适用。现在想着能不能减少数据线延时,但是数据是直接通过一个IBUFDS然后寄存的,可能加MAXDELAY约束也没什么用吧。期待大家的回复!

能否使用开发板上的FMC的IO,我觉得xilinx的开发板FMC接口的布线应该没问题的,我也是用xilinx的开发板(zedboard)FMC接口做的。