请教有符号数的计算

注意乘法近位不是是符号运算吗?哎

在数据相乘时,为什么要将负数当正数处理?

在数据相乘时,也是正常的带符号数相乘啊

就是工具自动将负数当成正数来进行相乘了。比如说-3*8. -3的二进制补码为1111_1101(十六进制为8'hfd),8的二进制为0000_1000(十六进制为8‘h08),而工具作处理时,就处理成十进制253*8,把8’hfd当成一个正数253来处理了。我后来只有把输入的数据作判断,当是负数时就把负数转换为正数,相乘后再转换为负数结果。难道必须这样处理?

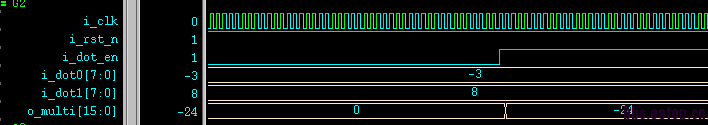

不是啊,举个例子 i_dot01 = -3, i_dot1 =8 ,o_multi=-24,不需要你自己去转化啊.verilog已经可以处理负数了啊

parameter UDLY = 1 ;

parameter BITS = 8 ;

input signed [BITS-1:0] i_dot0 ;

input signed [BITS-1:0] i_dot1 ;

input i_dot_en ;

input i_clk ;

input i_rst_n ;

output reg signed [2*BITS-1:0] o_multi ;

always @ (posedge i_clk or negedge i_rst_n)

if(~i_rst_n)

o_multi <= #UDLY 'h0;

else if(i_dot_en)

o_multi <= #UDLY i_dot0*i_dot1;

至于怎么转成补码进行计算那是软件去处理的东西,你写code的时候不需要自己人为的转化啊

你用的modelsim吧.我用的verdi,无法显示有符号数,只能显示十六进制。

我也用的verdi

verdi多强大的工具,怎么可能只显示十六进制

能否指点一下,怎么查看数据格式的选取。我先前找了很久都没找到。以前用modesim时就很好找。

waveform一列有个signal value radix 和signal value notation