Verilog缩减运算符的疑问

时间:10-02

整理:3721RD

点击:

夏宇闻那本verilog教程讲缩减运算符那一部分,与、或缩减运算都知道是怎么运算,但我就不知道那个“非”如何做缩减运算。大家有没有好的见解。

wire [7:0] a,b;

wire [7:0] res, res0, res1, res2;

wire res_1b;

assign a = 8'hf0;

assign b = 8'h1f;

//----按位运算

assign res = ~a; //res = 8'h0f;

assign res0 = a & b; //res = 8'h10;

assign res1 = a | b; //res1= 8'hff

assign res2 = a ^ b; //res2 = 8'hef;

//---缩减运算

assign res_1b = !a; //res_1b = 0

assign res_1b = |a; //res_1b = 1;

自己写个代码,用modelsim仿真一下,就明白啦。

“ !”是逻辑运算符吧!

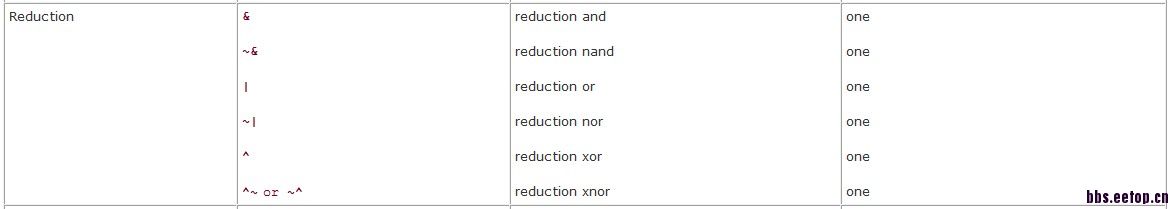

夏宇闻翻译的原版书籍中缩减运算符描述如下图所示,单独的“非”不是缩减运算符,应该不具有缩减功能,需要与其他运算符联合使用。

嗯,支持,!就是逻辑非,他的结果虽然对,但不是缩减运算的结果而是逻辑运算的结果。

三楼说得对,你的是逻辑非运算,我猜测夏宇闻那本书本意是取反~运算,不知是那本书有问题还是我没有领悟出非缩减运算的奥义。

这个解释比较合理,夏宇闻的“非”就是“取反”的意思。

那不就是退化为逻辑运算吗?

&、|是双目运算符,两位操作数运算后产生一位操作数,缩减了一位,以此类推最终产生一位结果。~是单目运算符,它如何缩减?

学习了。行行行行行行