请教RAM读写的问题

时间:10-02

整理:3721RD

点击:

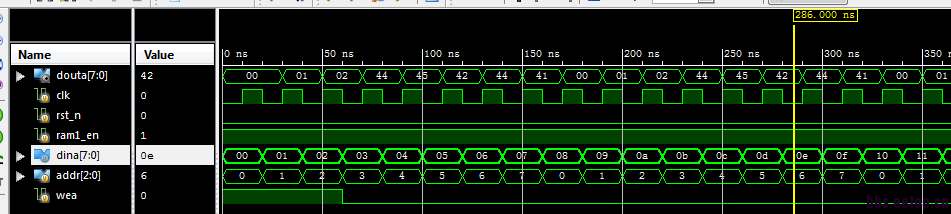

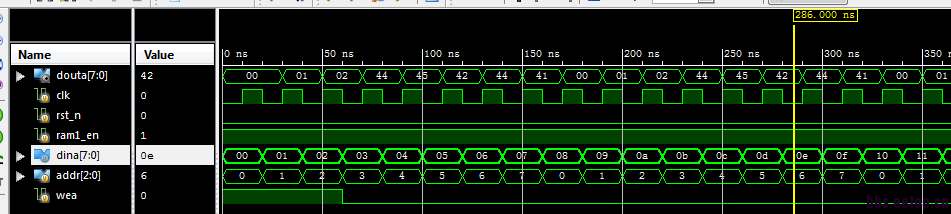

按照本论坛某位前辈的方法,新建了一块RAM,然后仿真,代码及结果如下,现在的问题是:

1.仿真的结果douta出来的数据和我初始化的数据对不上,这是为什么呢?2.dina数据是做什么用的?

请高手指教~

顶层文件:

module ram2(

input clk,input rst_n,

input ram1_en,

input [7:0] dina,

input [2:0] addr,

input wea,

output [7:0] douta

);

ram1 sp_ram (

.clka(clk), // input clka

.rsta(rst_n), // input rsta

.ena(ram1_en), // input ena

.wea(wea), // input [0 : 0] wea

.addra(addr), // input [2 : 0] addra

.dina(dina), // input [7 : 0] dina

.douta(douta) // output [7 : 0] douta

);

endmodule

测试文件:

module ramtest;

// Inputs

reg clk;

reg rst_n;

reg ram1_en;

reg [7:0] dina;

reg [2:0] addr;

reg wea;

// Outputs

wire [7:0] douta;

// Instantiate the Unit Under Test (UUT)

ram2 uut (

.clk(clk),

.rst_n(rst_n),

.ram1_en(ram1_en),

.dina(dina),

.addr(addr),

.wea(wea),

.douta(douta)

);

initial begin

// Initialize Inputs

clk = 0;

ram1_en = 1;

rst_n = 0;

dina = 0;

addr = 0;

wea = 1;

#60 wea = 0;

end

always #10 clk = ~clk;

always #20 begin dina <= dina + 1; addr <= addr+1; end

endmodule

初始化的coe文件:

MEMORY_INITIALIZATION_RADIX=2;

MEMORY_INITIALIZATION_VECTOR=

01001111,

01000010,

01000011,

01000100,

01000101,

01000010,

01000100,

01000001;

1.仿真的结果douta出来的数据和我初始化的数据对不上,这是为什么呢?2.dina数据是做什么用的?

请高手指教~

顶层文件:

module ram2(

input clk,input rst_n,

input ram1_en,

input [7:0] dina,

input [2:0] addr,

input wea,

output [7:0] douta

);

ram1 sp_ram (

.clka(clk), // input clka

.rsta(rst_n), // input rsta

.ena(ram1_en), // input ena

.wea(wea), // input [0 : 0] wea

.addra(addr), // input [2 : 0] addra

.dina(dina), // input [7 : 0] dina

.douta(douta) // output [7 : 0] douta

);

endmodule

测试文件:

module ramtest;

// Inputs

reg clk;

reg rst_n;

reg ram1_en;

reg [7:0] dina;

reg [2:0] addr;

reg wea;

// Outputs

wire [7:0] douta;

// Instantiate the Unit Under Test (UUT)

ram2 uut (

.clk(clk),

.rst_n(rst_n),

.ram1_en(ram1_en),

.dina(dina),

.addr(addr),

.wea(wea),

.douta(douta)

);

initial begin

// Initialize Inputs

clk = 0;

ram1_en = 1;

rst_n = 0;

dina = 0;

addr = 0;

wea = 1;

#60 wea = 0;

end

always #10 clk = ~clk;

always #20 begin dina <= dina + 1; addr <= addr+1; end

endmodule

初始化的coe文件:

MEMORY_INITIALIZATION_RADIX=2;

MEMORY_INITIALIZATION_VECTOR=

01001111,

01000010,

01000011,

01000100,

01000101,

01000010,

01000100,

01000001;

个人觉得你的激励有问题,你的复位没有撤销,所有的指令应该在复位撤销后在发送。

dina是写入的?似乎可以设置不要这个端口吧?