使用quartus进行编译,代码中定义的值与编译出的结果不一样

时间:10-02

整理:3721RD

点击:

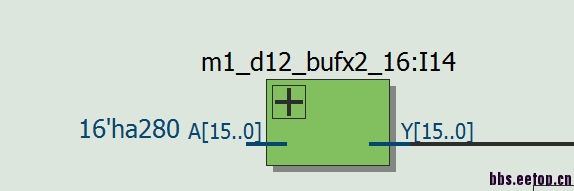

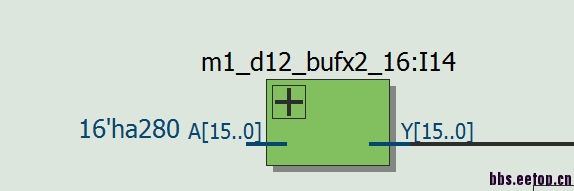

使用quartus进行编译,在程序中,编译某个buf的输入为16‘h0145(0000000101000101),m1_d12_bufx2_16 I14 ( .A(16'h0145), .Y(bit_time[15:0]));

但是在编译后查看RTL原理图,其显示的却是16'ha280(1010001010000000),这是什么原因导致的?

但是在编译后查看RTL原理图,其显示的却是16'ha280(1010001010000000),这是什么原因导致的?

看起来好像是bit swap了(MSB---LSB)

是的,请问你知道这是怎么回事儿嘛?第一次碰到这种问题...