点5分频实现

时间:10-02

整理:3721RD

点击:

奇数、偶数50%占空比分频很容易,点5分频是处理小数分频,比如3.5,7.5,23.5等,相比整数分频稍微复杂一点

- module Divclkp5(clk,tg_clk,rst);

- input clk,rst;

- output tg_clk;

- reg tg_clk;

- reg[23:0]counter,counter2;

- wire clk1;

- reg temp_tgp;

- parameter countN=11; //(2n+1)/2=clkin/clkout N=2n+1,n>=2

- always@(posedge clk or posedge rst)

- begin

- if(rst)

- counter<=24'b0;

- else if(counter>(countN-2))

- counter<=24'b0;

- else

- counter<=counter+1'b1;

- end

- //(countN-1)/2:(countN+1)/2

- always@(*)

- begin

- if(counter>(countN-3)/2)//counter odd

- temp_tgp<=1'b0;

- else

- temp_tgp<=1'b1;

- end

- //new clk

- assign clk1=clk^temp_tgp;

- //repeat count

- always@(posedge clk1 or posedge rst)

- begin

- if(rst)

- counter2<=24'b0;

- else if(counter2>(countN-3)/2)

- counter2<=24'b0;

- else

- counter2<=counter2+1'b1;

- end

- //注意Duty的调整,这里绝不会出现50%的情况

- //if N<9 <--(countN-5)/2) else <--(countN-1)/4

- always@(*)

- begin

- if(countN<9)

- begin

- if(counter2>(countN-5)/2)

- tg_clk<=1'b0;

- else

- tg_clk<=1'b1;

- end

- else

- begin

- if(counter2>(countN-1)/4)

- tg_clk<=1'b0;

- else

- tg_clk<=1'b1;

- end

- end

- endmodule

首先将分频数*2进行奇数分频,不需要占空比为50%,然后与原时钟xor得到新时钟,再用新时钟重计数

最后再来调整占空比

貌似1.5分频不适用,大家可以多多发言

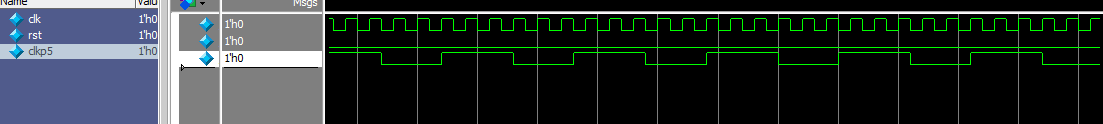

没看懂啊,为啥占空比是50,仿真结果不是6:5 么?

谢谢小编!好东西!

这位仁兄,我已强调.5分频是不存在占空比为50%的,占空比为一个周期内高电平所占比,计算为:Th/T,图中所示为3/5.5

之前也学过分数级的分频,但是不知道这种分频的实际用途是什么呢?求高手指点

我也没遇到过,就单独分频讲部分分频至少精确一点吧

那1.5分频的怎么写呢

请教下,有什么用吗?

直觉这样的时钟关系就是后端的噩梦,一般不会用的。

看代码n=1

我也不怎么用,只是一个想法。有时,想法是没有卵用的

小数分频是某些工程的基础,特别是一些特殊的锁相环处理,做时钟的常用!