modelsim版本不同仿真不同吗

确实是如此的,还是需要就具体问题来具体分析。

个人认为这种情况不应该出现,这样不就说明至少有一个软件有问题了吗!

恩,我也是这么觉得。我觉得ISIM肯定不会有问题,那么就说明10.0c的有问题

但是我感觉不应该啊,应该是软件的不稳定或者其他原因吧

ISE1.24不支持modelsim10.0,ISE10.0能调用modelsim10.1,但结果有时候出错!如果用modelsim10.1,最好用ISE13.4,回答完毕,我也遇到过类似问题。

modelsim的仿真结果跟ise的版本没有一点关系。

再说用ise调用modelsim实在不是一个好的选择。

碰到这种情况最好保存一下波形,然后比较一下,modelsim是可以比较波形文件的。

也不好说哪个对那个错,最好实际情况实际分析。一般来说高版本错误的可能性稍微小一点。

另外一个可能性就是小编的代码有问题。比方说下面的语法在不同的仿真器就有不同的行为。

代码综合没有问题,仿真有可能有问题。一般认为是编码风格问题 。

always @(posedge clk or posedge rst)

begin

if(rst)

a = 0;

else

a = b;

end

老版本的modelsim认为这个是一个非阻塞赋值,仿真没有问题。貌似ncsim也认为没有问题。

vcs就把这个认为是一个阻塞赋值。仿真结果和老版本的modelsim查一拍。

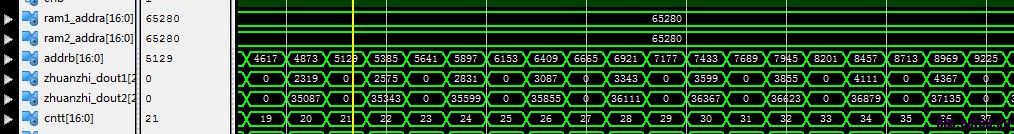

谢谢你的回答啊。我现在的问题是这样的,在modelsim6.5和ISIM中仿真图是这样的

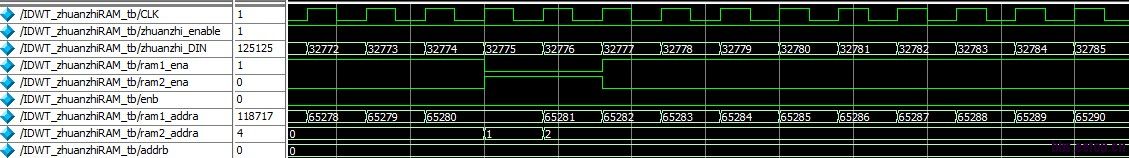

而在modelsim10.0c中是这样的

我本来设计的代码是希望按modelsim6.5显示的那样的结果。代码如下:

always@(posedge CLK)

if(zhuanzhi_enable)

begin

ram1_ena<=(ram1_addra==17'd65280)?1'b0:1'b1;

if(cntt==17'd256)

begin

ram1_addra<=ram1_addra+17'd257;

cntt<=17'd1;

end

else

begin

ram1_addra<=ram1_addra+1;

cntt<=cntt+1;

end

end

else

ram1_ena<=1'b0;

always@(posedge CLK)

if(addr_reset_write)

begin

ram1_addra<=ram1_addra;

在ram1_addra到65280的时候,之后一直是65280。不知到是不 是放在两个alway模块中了,10.0版本就出现问题了

看起来6.5是错的。不太确定,

你在代码中没有限定ram1_addra到65280以后就不继续增加了。

第二个always块是什么意思,ram1_addra <= ram1_addra ?

不至于吧,我没有试过,是不是因为其它设置不一样呢

就是在第二个always模块中规定的ram1_addra等于65280时,一直保持65280这个数。这个代码我在6,5和ISIM中仿真都是图1的结果,跟我预想的也一样,在10.0中就出现图2的结果了,在65280的时候,只保持了两个始终。

你觉得是我代码上出问题了吗?如果要对ram1_addra设定一直重复65280的话,是要放在一个always中吗?

第二个always块就是为了是ram1_addra一直维持65280这个数啊,

我在想是不是10.0版本中不允许放在两个always模块中啊?但是6.5和ISIM是可以的啊。

always@(posedge CLK)

if(zhuanzhi_enable)

ram1_ena<=(ram1_addra==17'hff00)?1'b0:1'b1;

else

ram1_ena<=1'b0;

always@(posedge CLK)

if(zhuanzhi_enable)

begin

if(cntt==17'h100)

begin

cntt<=17'd1;

end

else

begin

cntt<=cntt+1;

end

end

else ;

always@(posedge CLK)

if(zhuanzhi_enable)

begin

if(cntt==17'h100)

begin

ram1_addra<=ram1_addra+17'h101;

end

else

begin

ram1_addra<=ram1_addra+1;

end

end

else;

always@(posedge CLK)

if(addr_reset_write)

begin

ram1_addra<=ram1_addra;

你这个地方属于多重赋值。

两个always块里面都有对ram1_addra的赋值。

第二个图里面zhuanzhi_enable 一直是1,一直在变是正确的啊

搞了七八天,软件卸了装装了卸,总算是把ISE和modelsim整合到一起了。试来试去,感觉上述问题真的是版本的问题,可能是10.0d对verilog语法要求更为严格。可是可是?我该按照ISIM和之前的版本还是按照10.0d的版本啊!事情真是一桩接着一桩啊!

重大消息::

我刚才在10.0d的modelsim.ini文件中将自动优化去掉了,猜怎么着?哈哈!结果和6.5及ISIM版本的一样啦!说明我上述的语法完全是正确的。可谓是经验啊!提供给大家,愿者分享!

我是菜鸟,modelsim的版本和altera的modelsim对应的版本如何对应?

这是由于你代码风格不好,导致程序优化结果不一样.所以改好你的代码风格吧,否则综合的时候一样可能会有这样的问题

oh,那我win7 64位系统使用什么版本的modelsim好一些啊

第二个always是怎么会,“ram1_addra<=ram1_addra”;不能将一个reg 变量仿真两个always中进行赋值操作,10最近也在用,感觉和6.5没什么区别。

mark mark

如果你的语法正确,仿真结果应该一样

恩,是的。现在好了,原因是新版本modelsim配置文件中将优化没有去掉。

不要在两个always里对同一个信号赋值。

千万不要。

即使在TB里也不要。

养成好习惯,否则吃大亏。

还真有可能

学习中!

最好还是一个 sequential always 对应一个 variable,不容易出问题,也就省了多天的折腾。

24L正解,先去看看代码风格,仅能编译通过的Verilog离真正的硬件还有段距离。

这个是有问题的,ram1_addra出现在两个always的块中,这就算仿真通过了,在ise中综合也会通不过的,需要好好的更改自己的编程风格,这个可以参考华为的编程规范

学习了,编码风格