全局时钟走线不同版本延时不同

时间:10-02

整理:3721RD

点击:

背景:使用进位链来构成延时链,比较关注不同版本下延时的固定性。

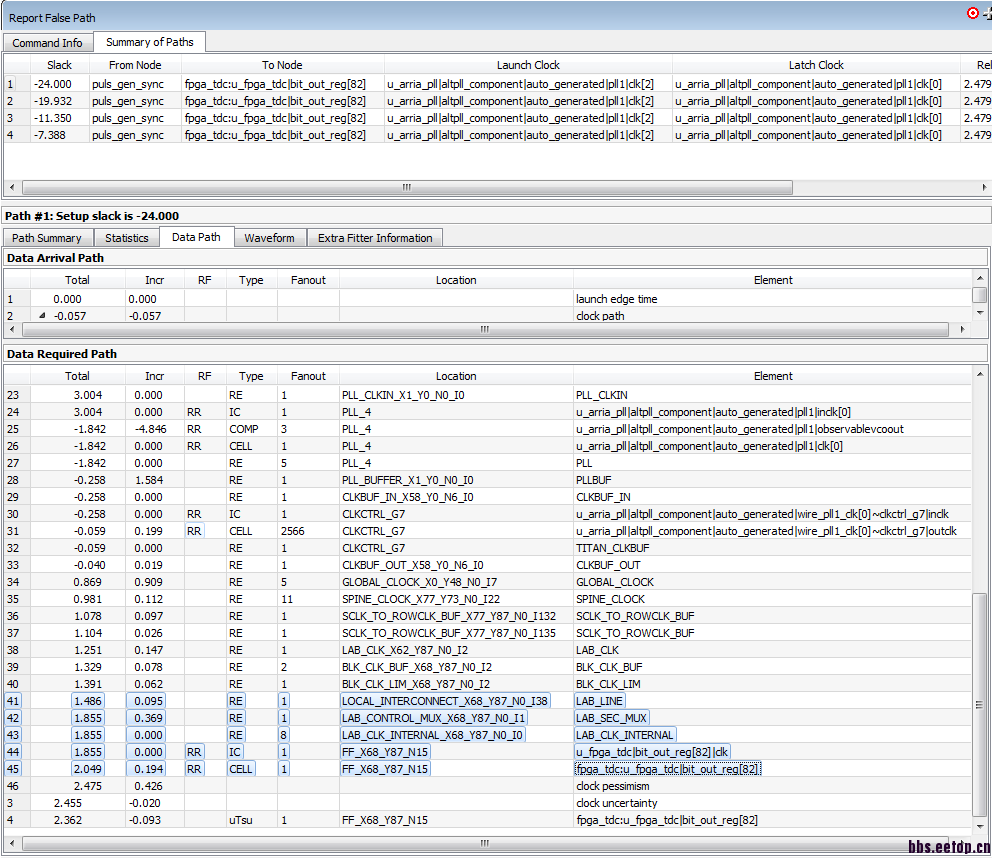

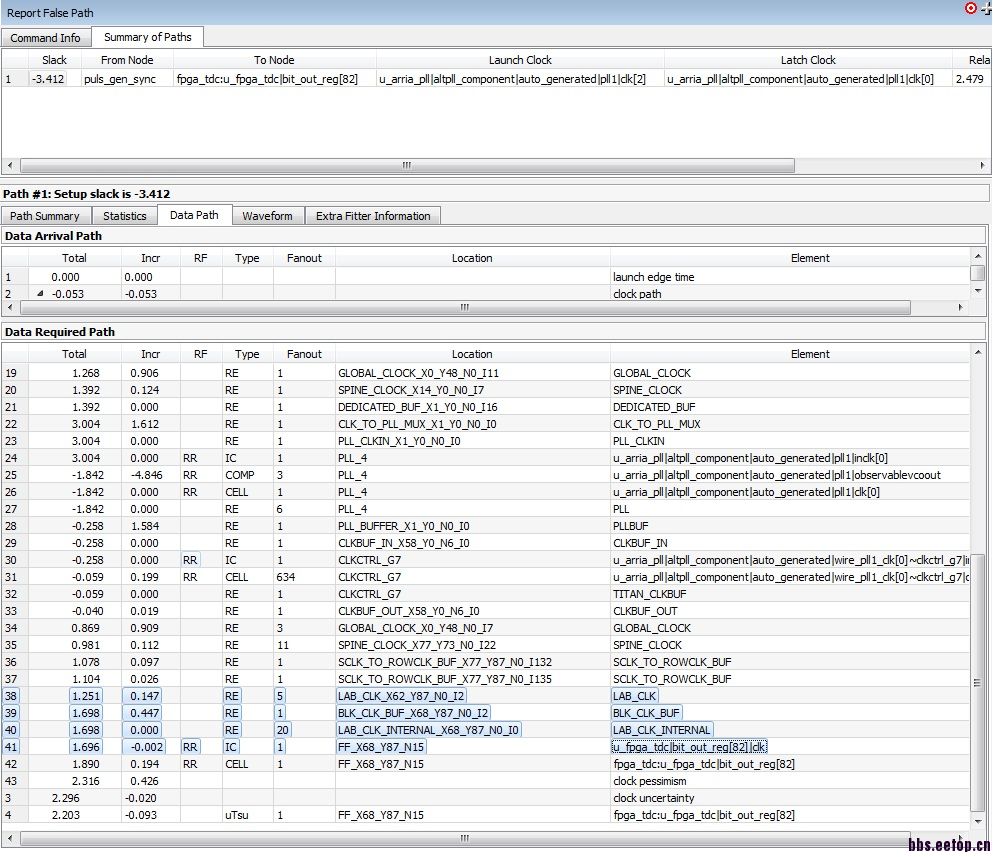

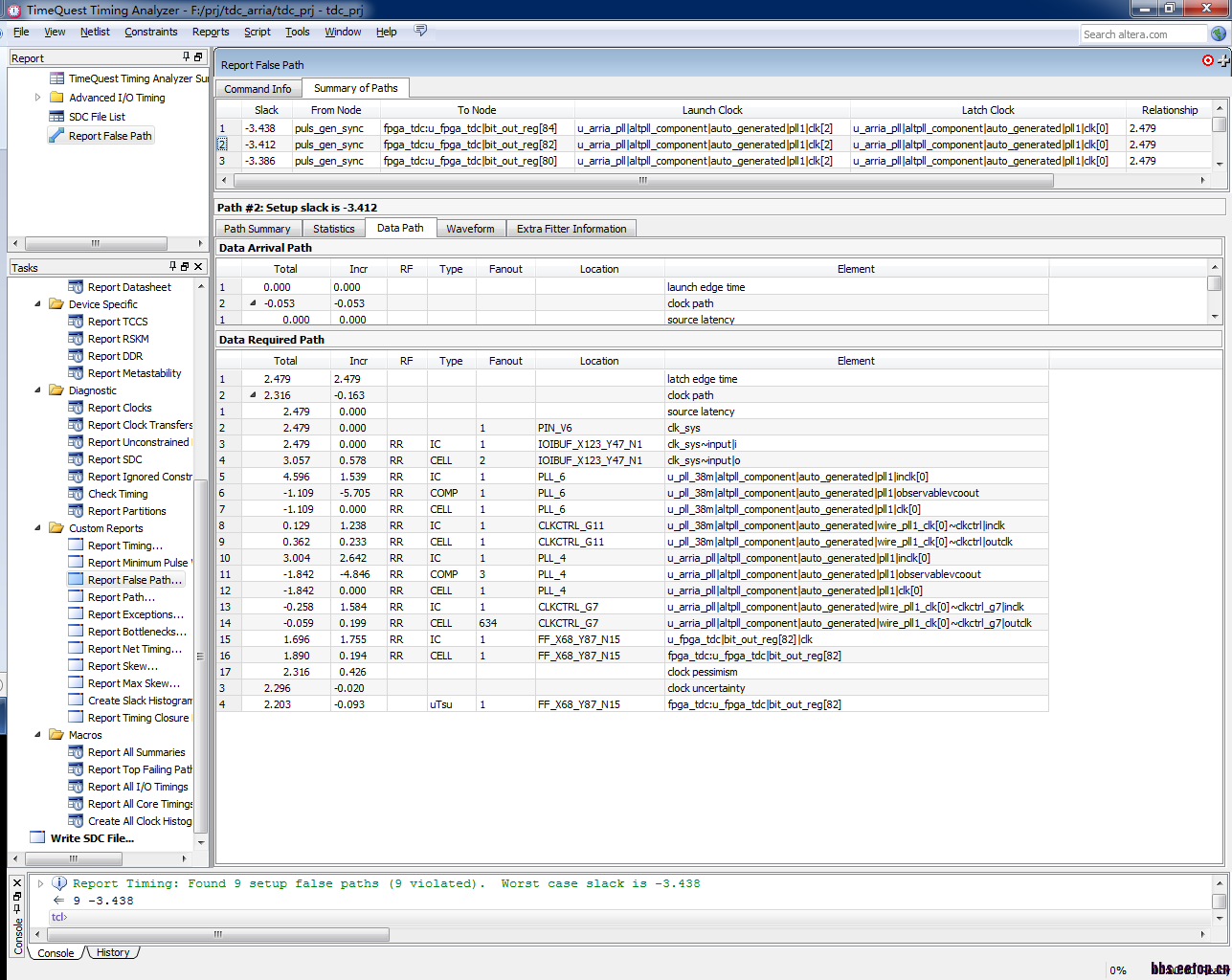

时钟已经上了全局,并做了约束,上G7,不同版本发现,对于同一个寄存器,从G7_CTRL到寄存器的时钟走线延时不同,想请教一下这是为什么呢?已经成功上了全局,走线路径就已经固定了吧,为什么不同版本,延时还会有变化呢?

具体的路径延时情况看附件。我应该怎么做才能保证时钟走线延时每次都一致呢?

求救各位大侠!

时钟已经上了全局,并做了约束,上G7,不同版本发现,对于同一个寄存器,从G7_CTRL到寄存器的时钟走线延时不同,想请教一下这是为什么呢?已经成功上了全局,走线路径就已经固定了吧,为什么不同版本,延时还会有变化呢?

具体的路径延时情况看附件。我应该怎么做才能保证时钟走线延时每次都一致呢?

求救各位大侠!

帮你顶起来

多谢兄台!

求助!

哪位大神可以解释一下?扫个盲!

求助!

求助!

后端的貌似懂得人少一点

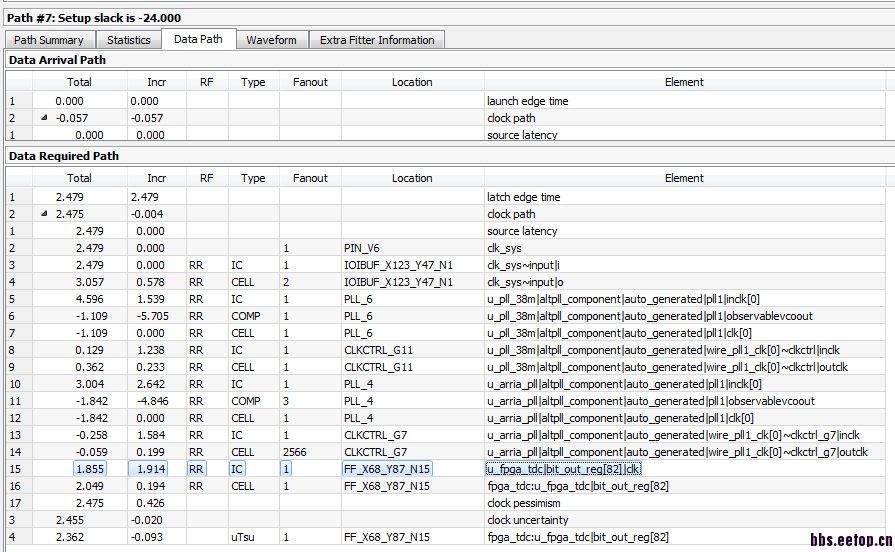

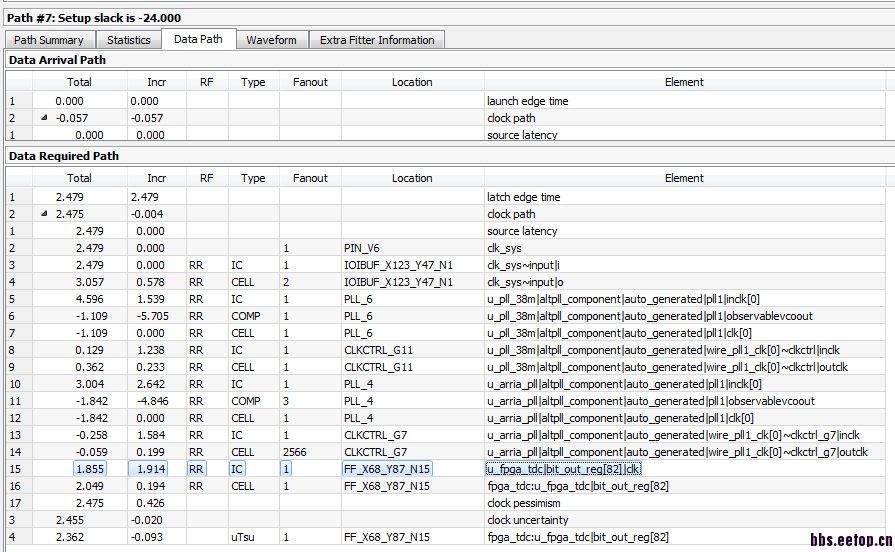

两个时钟延时不同是因为两个布线结果中,CLKCTRL_G7的驱动数不同,一个为2566,一个为634.虽然,硬件中使用的路径是一致的但是,由于驱动数较多时,容性负载增加,会导致延时增加。导致驱动数不同,应该是不同版本综合结果的不一致导致的。

非常感谢!我还想问一下,驱动数增加,容性负载增加,但是有的寄存器的延时是没有变的,有的是增加了的,也就是两个寄存器时钟走线skew也在变,我的意思是理论上,要增加,应该都增加吧?

非常感谢!我还想问一下,驱动数增加,容性负载增加,但是有的寄存器的延时是没有变的,有的是增加了的,也就是两个寄存器时钟走线skew也在变,我的意思是理论上,要增加,应该都增加吧?

[attach]625676[/attach][attach]625675[/attach]

[attach]625676[/attach][attach]625675[/attach]

已解决。

原因:全局时钟走线的物理路径并不是唯一的,即使对于同一个寄存器,时钟走线也可能不同,扇出不同可能引起时钟走线不同。这个可以通过在查看路径时,打开"show routing"就可以看到。