请教:用verilog怎么实现图中波形?

时间:10-02

整理:3721RD

点击:

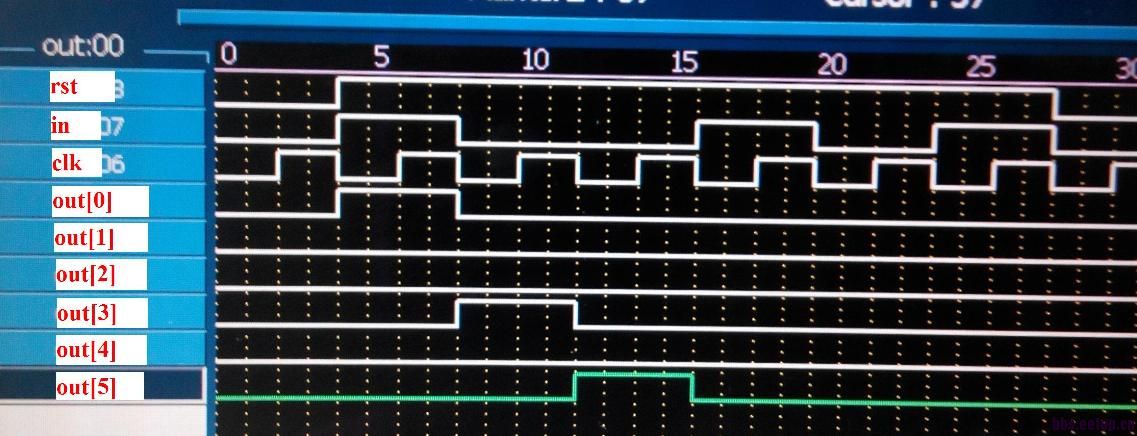

怎么用verilog或vhdl来实现图中的波形结构。

输入clk、rst、in(图中以”100101“为例),输出out0、out1...out5对应in有效6位,并且高电平1是依次排下去的。

谢谢各位高手对我这初学者的指点

这个图形有问题,在时刻10的时刻还不知道后边来的数据,怎么就输出了呢,如果按照你的逻辑是可以输出的,但输出要滞后,在整个数据完成后才能输出out

低电平复位,下降沿有效的移位寄存器?

有这种可以预测后面输入序列的电路吗? 我想见识一下

确实,怎么in直接就到第一个out【0】了

波形中out直接由in在第一个posedge clk 直接到out,这个不对吧,应该是个移位寄存器,不过好像波形补全最好

同意2楼;in应该是6bit的并行输入吧

是相当于移位寄存器,正如前面有人说的,有点问题。怎么数据还没到,就已经有输出了