Quartus Create Generated Clock 与 Create Clock 差别?

1.晶片外部输入的时钟源?

2.PLL 产生的时钟源?

3.寄存器递减产生的时钟源?

请问 Create Generated Clock 与 Create Clock 要怎么设?

Create Clock 是创建时钟源

Create Generated Clock有两种功能:传播你命令里约束的时钟,同时打断经过此路径的别的时钟

还有个常用的set_clock_groups用于划分时钟域

另外你的问题:

1.比如外部输入时钟端口CLK,周期为10ns

create_clock -p 10 [get_ports CLK]

(端口有数据传输还要设input/output delay)

2. derive_pll_clocks

3. 比如用寄存器clk_div对输入端口CLK进行二分频:

create_generated_clock -source [get_ports CLK] -divide_by 2 [get_registers clk_div]

跑的时候留意有无STA相关Warning(通常是由于SDC约束写的有问题),跑完看看时序有无Violation。

1.((比如用寄存器clk_div对输入端口CLK进行二分频:))问题我在 Quartus ii 找不到我的寄存器2分频的NET线 ?

2.input delay 我设定与第一组PLL.c0 有关的NET线,最后RUN及save sdc,但是 sdc档案居然没半条?

我分频例子里用的是get_registers你就跟用嘛,不会坑你的,永远别用get_nets...

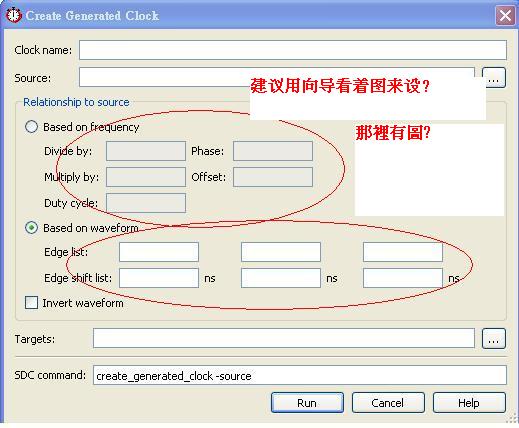

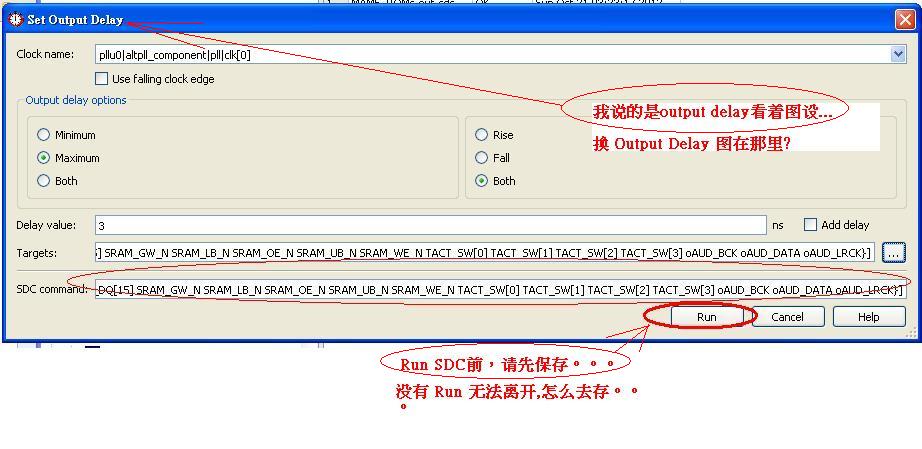

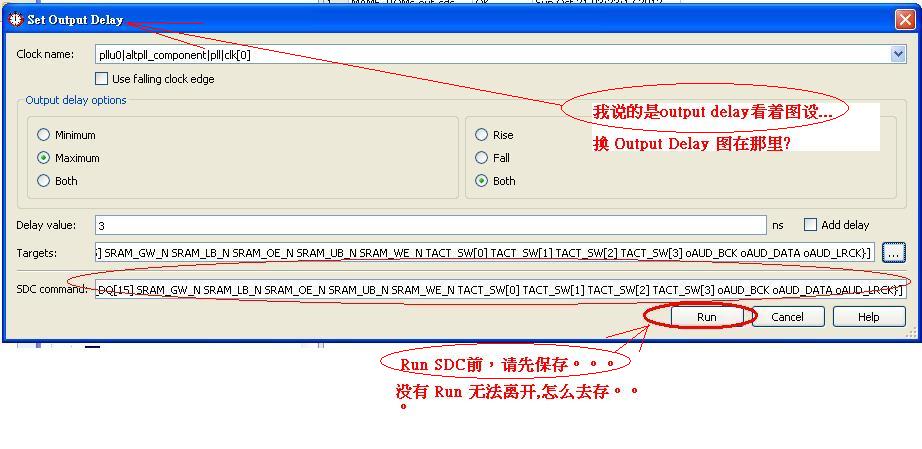

input/output delay只能针对端口上的时钟,用get_clocks,从端口输入一般create_clock,从端口输出的一定要create_generated_clock,另外output delay设法(你可能会觉得)比较奇怪,建议用向导看着图来设。

注意save时的文件名,把.out去掉,不要expand。

你 也没用,SDC格式又不是Altera定的。换成PT你的设法一样不能跑。

Create Generated Clock 自古到今没有图...

除非你从主菜单选才有 TimeQuest Timing Analyzer 建立时才有

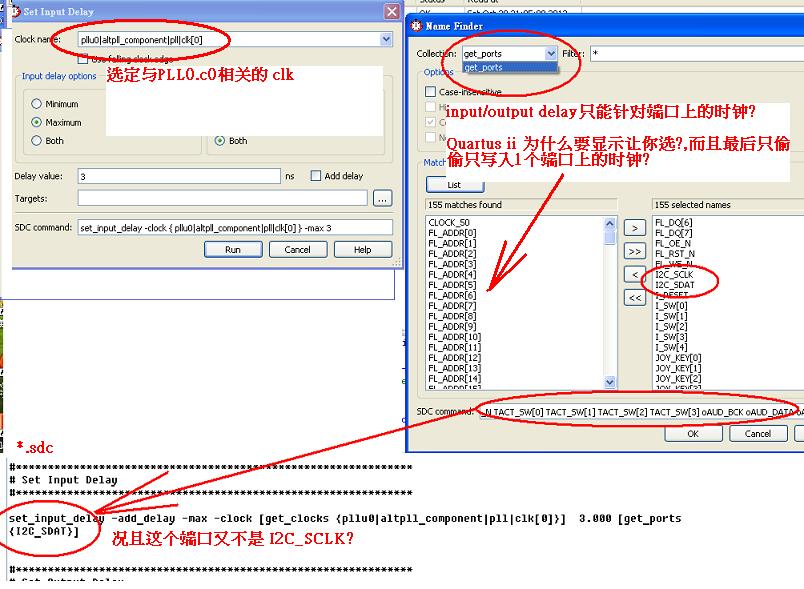

TimeQuest Set Input Delay 更是白痴极的设定

SDC comnand 命令有..RUN...最后只存一个 i2c_sdat至*.sdc档,其他都是假的?让你选到死...白痴软件

我说的是output delay看着图设,向导在TimingQuest某个菜单下第一项。

input/output delay时钟不针对端口时钟约束就没有实际意义,并不是说这样设在物理上不可行。

input delay是个“已知条件”,比如已知输入端口CLK和输入数据DQ[7:0]有相位关系:DQ相对CLK最少延后1ns,最大延后2ns,我们就先在CLK端创建时钟:

- create_clock -p 10 [get_ports CLK]

再定义输入数据端口相位关系:

- set_input_delay -min -clock [get_clocks CLK] 1 [get_ports DQ[*]]

- set_input_delay -max -clock [get_clocks CLK] 2 [get_ports DQ[*]]

(这里可以用通配符,不用拉一大堆端口进来。)

工具再根据这个“已知条件”,进行内部时序收敛。

假如你这个“已知条件”就是错的,工具计算的结果肯定也是错的。比如你用内部的一个PLL时钟和外部一堆输入端口定义时序关系,但实际上它们并不存在任何时序关系。这样定义出来有何意义呢?

Node Finder也只是给出get_ports等命令可以达到的节点,真正哪个节点是有意义的只有设计者才知道,工具是不可能知道的。正如综合器可以帮你检查语法对不对,但永远不知道你写的内容对不对。

Run SDC前,请先保存。

TimeQuest已经是世界上最简单易用的STA工具了。虽然上手也需要几天。不信你就去跑跑PrimeTime,估计你半小时就吐血了。

刚开始接触STA和TimeQuest,从您的帖子中学习了

你说完全与quartus ii 不一样,你就传图上来看看

input/output delay时钟不针对端口时钟约束就没有实际意义,并不是说这样设在物理上不可行。

那麼 Quartus ii 顯示出來還讓你選?選完也沒有任何警告訊息,...選假的嗎?好玩嗎?還是選好看的 ?

我贴Quartus ii 你真的会吐血(有图有真像,无图无真像)

另外参考其他博客论坛

http://bbs.ednchina.com/BLOG_ARTICLE_198929.HTM

对于逻辑单元分频的时钟信号,也可以采用命令create_generated_clock会更加精确。

但是逻辑单元分频与寄存器分频不同

逻辑单元分频例:48MHZ分频1次得到的时钟为 24 MHZ

create_generated_clk -48Mclk -source [getports sysclk] -div 1 [get_registers cnt0_clk]

但是寄存器分频该怎么设?48MHZ 怎么分频设 4MHZ? -div ?

有图有真像,无图无真像

你看看我是怎么回你的。

“另外output delay设法(你可能会觉得)比较奇怪,建议用向导看着图来设。”

“我说的是output delay看着图设,向导在TimingQuest某个菜单下第一项。”

我就问一个,向导你找到了吗?我说的向导是这个:

http://quartushelp.altera.com/11.1/mergedProjects/analyze/sta/sta_com_sta_wizard.htm

家里电脑没装Quartus,确实无图无真相。我上面例子都比较简明了,你觉得我说错了可以去听别人的,不拦你。

大侠的图木有看懂