(axi-stream接口)RGB2LUV颜色空间转换IP问题请教

时间:10-02

整理:3721RD

点击:

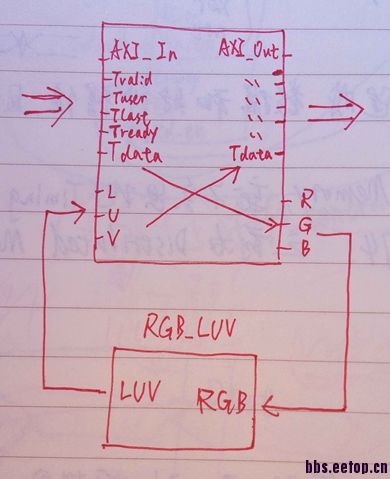

我在做一个RGB到LUV颜色空间转换的IP核,是用的AXI-STREAM的接口,输入为RGB的图像数据(视频),示意图如下:

先将输入AXI-IN中的数据Tdata(RGB)取出,转化到LUV后作为AXI-OUT中的Tdata输出。RGB_LUV这个IP有23个时钟的延迟。

输出图像中有大量噪声,这个思路是否可行?或者有什么改进的方法?噪声是axi -stream接口时序有问题造成的还是RGB2LUV那一部分造成的? 望大家指教。

以下为图中上面一个IP的代码:

- entity process_test is

- port

- (

- CLK : in std_logic;

- RSTN : in std_logic;

- TUSER_in : in STD_LOGIC;

- TLAST_in : in STD_LOGIC;

- TVALID_in : in STD_LOGIC;

- TREADY_in : out STD_LOGIC;

- TDATA_in : in STD_LOGIC_VECTOR(23 downto 0);

- RGB_out : out STD_LOGIC_VECTOR(23 downto 0);

-

- L_in : in STD_LOGIC_VECTOR(7 downto 0);

- U_in : in STD_LOGIC_VECTOR(7 downto 0);

- V_in : in STD_LOGIC_VECTOR(7 downto 0);

- TUSER_out : out STD_LOGIC;

- TLAST_out : out STD_LOGIC;

- TVALID_out : out STD_LOGIC;

- TREADY_out : in STD_LOGIC;

- TDATA_out : out STD_LOGIC_VECTOR(23 downto 0)

- );

- end process_test;

- architecture Behavioral of process_test is

- begin

- TREADY_in <= TREADY_out;

- --将AXI-In的RGB数据输出

- RGB_out(23 downto 0) <= TDATA_in(23 downto 0);

- process(CLK,RSTN)

- begin

- if rising_edge(CLK) then

- TVALID_out <= TVALID_in;

- TUSER_out <= TUSER_in;

- TLAST_out <= TLAST_in;

- end if;

- end process;

- --将转换后的LUV数据作为Tdata_out输出

- TDATA_out(7 downto 0) <= L_in(7 downto 0);

- TDATA_out( 15 downto 8) <= U_in(7 downto 0);

- TDATA_out(23 downto 16) <= V_in(7 downto 0);

- end Behavioral;

VHDL阅读有困难。