IO timing constrainingde

时间:10-02

整理:3721RD

点击:

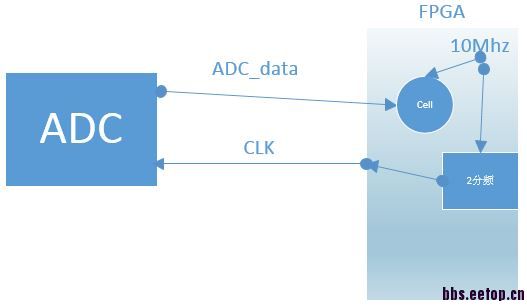

FPGA 内部有个10Mhz的时钟 经过2分频产生了ADC的工作时钟,

ADC_data 输入到FPGA 中后第一级寄存器是在10Mhz时钟下进行操作的。

问题, 在对ADC_data进行set_input_delay设置时候 参考时钟应该 用哪个呢?

ADC发送数据用的5Mhz时钟 还是 在FPGA中采样ADC_data数据的时时钟呢?

个人两个矛盾的观点

1.用5Mhz时钟是因为 set_input_delay 中计算 延时的参数 用的是5Mhz时钟线的长度 所以用5Mhz

2.但我们做 set_input_delay 的目的是希望timing analyser 能够根据端口上的数据延时 来进行内部布线 保证数据到达FPGA内部的第一级寄存器的建立和保持时间 都满足要求 在这个设计中第一级寄存器的工作时钟是10Mhz 所以用10Mhz

我快人格分裂了 求大神指教!

还是 没搞清楚 到底 设置参考时钟的 时候要 以launch为准呢 还是 latch时钟为准呢

用的是什么ADC?5M的时钟送10M的数据?

我觉得应该是5M的时钟,并且在5M的时钟采样,再跨频处理到10M

谢谢 这么做就能消除这个问题了 其实之前的做法 太跳了