关于modelsim和matlab协仿真的问题,用的是verilog语言。

时间:10-02

整理:3721RD

点击:

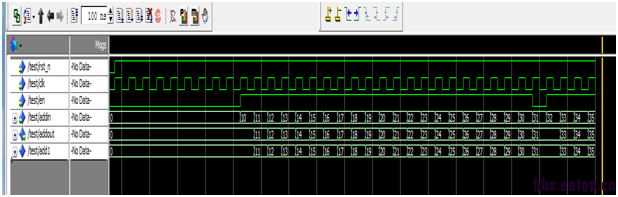

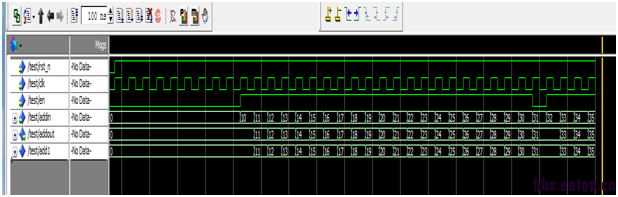

问题:用vhdl语言和Verilog语言和matlab协仿真同一个程序,在modelsim上跑出来的结果不一样。导致时序有问题。网上查了很多资料没有结果。(调用的.m函数一样即输入信号一样)。

例子: 带使能信号和复位信号的加法器,由matlab给输入数据addin,en。

错误: VHDL仿真结果貌似是正确的,但是verilog语言仿真的结果addout应该延时输入的addin一个clk,为什么没有延时呢。!

1. VHDL语言:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test is

port

(

rst_n : in std_logic;

clk : in std_logic;

en : in std_logic;

addin : in std_logic_vector(11 downto 0);

addout : out std_logic_vector (11 downto 0)

);

END test;

architecture rtl of test is

signal add1 : std_logic_vector(11 downto 0);

begin

process(clk,rst_n)

begin

if rst_n ='0' then

add1<=(others=>'0');

elsifclk'event and clk = '1' then

if en = '1' then

add1<=addin+'1';

else

add1<=add1;

endif;

end if;

end process;

addout<=add1;

end architecture;

2. Verilog语言

module test (clk,

rst_n,

addin,

en,

addout

);

input clk;

input rst_n;

input en;

input [11:0] addin;

output [11:0] addout;

reg [11:0] add1;

assign addout=add1;

always @ (posedge clk)

begin

if (!rst_n)

begin

add1=12'h0;

end

else if(en)

begin

add1=addin+1;

end

end

endmodule

例子: 带使能信号和复位信号的加法器,由matlab给输入数据addin,en。

错误: VHDL仿真结果貌似是正确的,但是verilog语言仿真的结果addout应该延时输入的addin一个clk,为什么没有延时呢。!

1. VHDL语言:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test is

port

(

rst_n : in std_logic;

clk : in std_logic;

en : in std_logic;

addin : in std_logic_vector(11 downto 0);

addout : out std_logic_vector (11 downto 0)

);

END test;

architecture rtl of test is

signal add1 : std_logic_vector(11 downto 0);

begin

process(clk,rst_n)

begin

if rst_n ='0' then

add1<=(others=>'0');

elsifclk'event and clk = '1' then

if en = '1' then

add1<=addin+'1';

else

add1<=add1;

endif;

end if;

end process;

addout<=add1;

end architecture;

2. Verilog语言

module test (clk,

rst_n,

addin,

en,

addout

);

input clk;

input rst_n;

input en;

input [11:0] addin;

output [11:0] addout;

reg [11:0] add1;

assign addout=add1;

always @ (posedge clk)

begin

if (!rst_n)

begin

add1=12'h0;

end

else if(en)

begin

add1=addin+1;

end

end

endmodule

另外附上.m文件。即输入的激励

这是我给的m文件,即输入的激励:

function [iport,tnext] = test(oport, tnow, portinfo)

tnext=[];

iport=struct();

persistent inc;

persistent rst;

CLK_PERIOD = 1e-8;

RST_MUL_TIME = 5;

RST_TIME = RST_MUL_TIME * CLK_PERIOD;

if isempty(inc)

inc=0;

iport.addin=dec2bin(0,12);

iport.en=dec2bin(0,1);

end

inc =inc+1;

if tnow <= RST_TIME

rst = dec2bin(0, 1);

inc=[];

else

rst = dec2bin(1, 1);

end

if inc>=10

iport.addin=dec2bin(inc,12);

iport.en=dec2bin(1,1);

end

if 30==mvl2dec(oport.addout)

iport.en=dec2bin(0,1);

end

iport.rst_n=rst;

end

看一看,学一学!

xuexixuexi

非常感谢!

应该是仿真输入信号驱动时刻的原因

仿真都是clk上升沿请求.m。VHDL和verilog使用的是一样的请求函数。 不知道是不是matlab对verilog的仿真功能还没有健全。我还是不懂啊