用Verilog如何实现上升沿开始计数,下降沿停止计数

用边沿检测,posedge(上升沿),negedge(下降沿)

你需要一個更高頻且穩定的sampling clock做偵測上升緣及下降緣的偵測及計算時間。

always@(posedge clk or negedge rst) beign

if(~rstn) begin

delay[1:0] <= 2'd0;

end

else begin

delay[1:0] <= {delay[0],pluse};

end

end

wire pluse_start = (~delay[1])& delay[0] ;

wire pluse_end = ( delay[1])& (~delay[0]) ;

然后使用pluse_start和pluse_end作为脉冲pluse的开始和停止计数标志。

写的不错呀。学习!

上升沿触发 下降沿停止方法比较多,上升沿触发,下个上升沿截止该怎么弄?

根据另一个帖子,liqz大神写的程序改的,

module Pulse_Width(

clk,

rst_n,

signal

pwcounter

);

input clk, rst_n, signal;

output signed [9:0] pwcounter;

reg [9:0] pwcounter;

reg signal_reg;

reg state;

always @ (posedge clk )

begin

if(!rst_n)

begin

pwcounter<=10'd0;

signal_reg<=1'd0;

state<=1'd0;

end

else

begin

signal_reg<=signal;

case(state)

1'd0:

begin

if(signal&(~signal_reg))

begin

state<=1'd1;

pwcounter<=pwcounter+1'd1;

end

end

1'd1:

begin

if(signal_reg&(~signal))

begin

state<=1'd0;

pwcounter <=10'd0;

end

else

counter<=counter+1'd1;

end

endcase

end

end

endmodule

求教其中state的作用是?

如果clk跟signal是不同步的,要注意metastable的問題。

请问上升沿触发,下个上升沿截止该怎么弄?

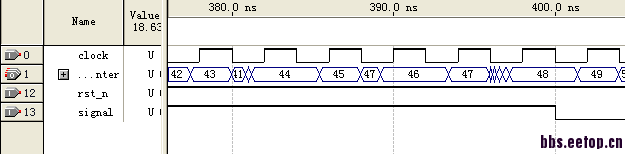

按7楼那么写仿真如上图,是不同步的问题吗?

數位仿真看不出來metastable的問題。

從waveform看來,你是用clock負緣計數counter嗎?

如果是,看起只是counter的每個bit的transition time不同,你有掛SDF去仿真嗎?

感谢!

所谓的7楼代码,和我的是一个原理,你应该好好看看我的代码,了解了这段代码的核心,就不会纠结哪里开始哪里结束了。

看了你的代码,上升沿和下降沿都可以表示成变量,就可以直接控制起始了,但是测周期的话,起始截止都是上升沿,是不是要引入新变量?初学者可能表述不清,不好意思哈~以下是我根据一段程序改的测周期,编译的时候提示cnt有错误,(Error (10133): Verilog HDL Expression error at Period.v(26): illegal part select of unpacked array "cnt"),能麻烦您帮忙看下么?

module Period(

clk,

rst_n,

signal,

percounter

);

input clk, rst_n, signal;

output signed [9:0] percounter;

reg [9:0] percounter;

reg signal_reg;

reg cnt[9:0];

wire signal_pos;

always @ ( posedge clk or negedge rst_n ) begin

if ( !rst_n ) begin

signal_reg <= 1'b0;

end

else begin

signal_reg <= signal;

end

end

assign signal_pos = signal & (~signal_reg);

always @ ( posedge clk or negedge rst_n ) begin

if ( !rst_n ) begin

cnt[9:0] <= 10'd0;

end

else if ( signal_pos == 1'b1 ) begin

cnt[9:0] <= 10'd0;

end

else begin

cnt[9:0] <= cnt[9:0] + 10'd1;

end

end

always @ ( posedge clk or negedge rst_n ) begin

if ( !rst_n ) begin

percounter[9:0] <= 10'd0;

end

else if ( signal_pos == 1'b1 ) begin

percounter[9:0] <= cnt[9:0];

end

else begin

end

end

endmodule

将时钟取反,阔步阔以?

测周期的话,不就是两次检测到上升沿的时间段吗?你设一个变量记录一下不就很简单的算出来了吗。