关于vhdl的信号和变量以及Verilog的阻塞和非阻塞赋值的一些思考

时间:10-02

整理:3721RD

点击:

最近在看Xilinx公司的ug687-xst-userguide,里边有这样一段程序: signal count_r : std_logic_vector(2 downto 0) := (others => '0');

process(a)

begin

count_r <= "000";

for i in 0 to 7 loop

if (a(i) = '0') then

count <= count + 1;

end if;

end loop;

count <= count_r;

end process;

我给仿真了一下,发现count在每次a变化的时候就加1,而不是计算a中0的个数,百思不得其解。

然后尝试将signal改为variable,如下:

process(a)

variable count_r : std_logic_vector(2 downto 0);

begin

count_r := "000";

for i in 0 to 7 loop

if (a(i) = '0') then

count <= count + 1;

end if;

end loop;

count <= count_r;

end process;

仿真结果正确。

这让我想到了Verilog里的阻塞和非阻塞赋值,代码如下:

always @ (a) begin

cnt = 0;

//cnt <= 0;

for(i=0;i<8;i=i+1)begin

if(a[i] == 1'b1)begin

cnt = cnt + 1;

//cnt <= cnt + 1;

end

end

end

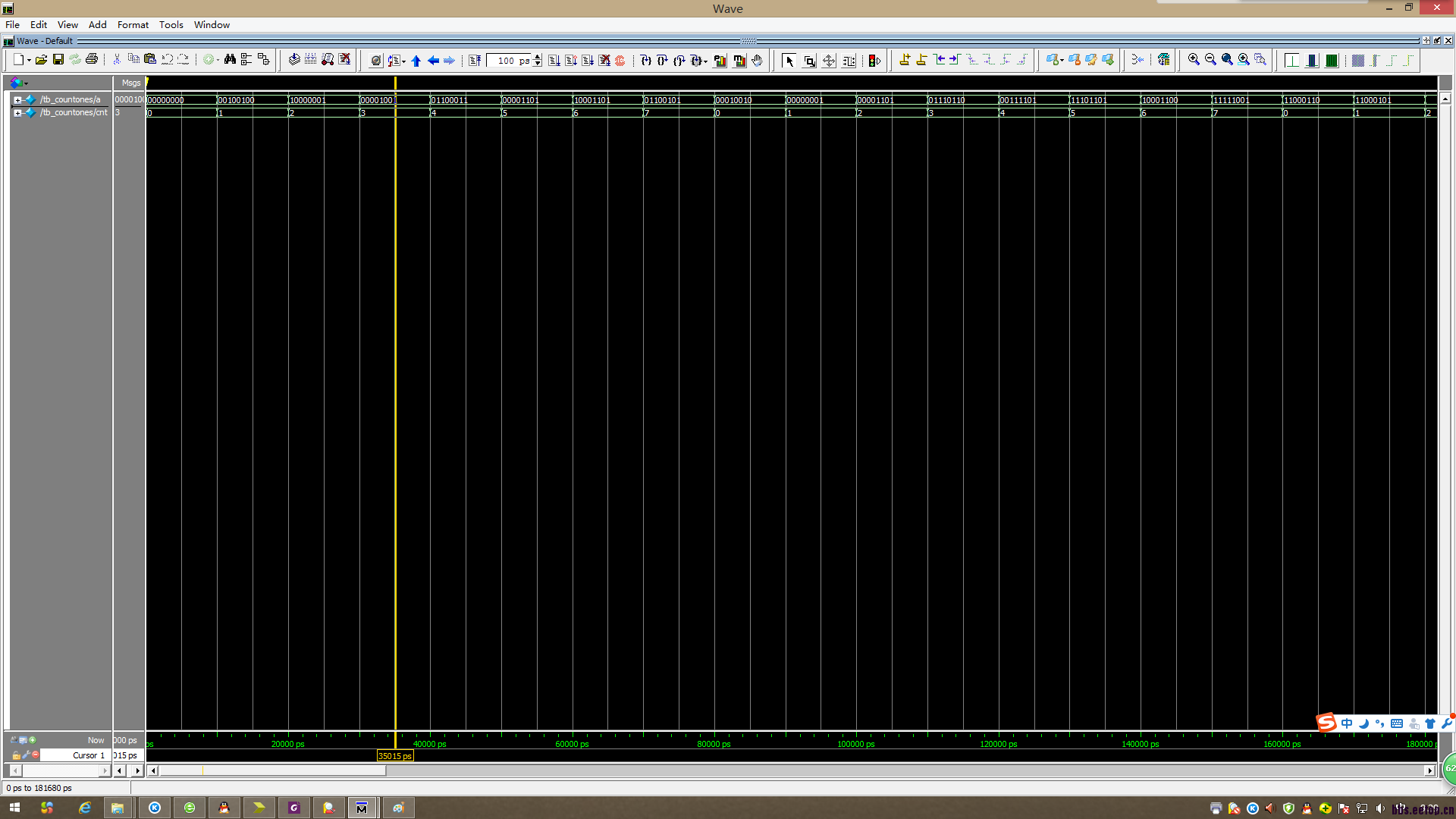

当采用非阻塞赋值时,结果和vhdl里用信号赋值一样;

当采用阻塞赋值时,结果和vhdl里用变量赋值一样,功能正确。

Verilog里的阻塞和非阻塞赋值让很多初学者都很纠结,觉得无法理解,个人觉得这对了,连Xilinx的大神们在写文档里的程序的时候

也是随心所欲,会有考虑遗漏的时候,更何况我等初哥

process(a)

begin

count_r <= "000";

for i in 0 to 7 loop

if (a(i) = '0') then

count <= count + 1;

end if;

end loop;

count <= count_r;

end process;

我给仿真了一下,发现count在每次a变化的时候就加1,而不是计算a中0的个数,百思不得其解。

然后尝试将signal改为variable,如下:

process(a)

variable count_r : std_logic_vector(2 downto 0);

begin

count_r := "000";

for i in 0 to 7 loop

if (a(i) = '0') then

count <= count + 1;

end if;

end loop;

count <= count_r;

end process;

仿真结果正确。

这让我想到了Verilog里的阻塞和非阻塞赋值,代码如下:

always @ (a) begin

cnt = 0;

//cnt <= 0;

for(i=0;i<8;i=i+1)begin

if(a[i] == 1'b1)begin

cnt = cnt + 1;

//cnt <= cnt + 1;

end

end

end

当采用非阻塞赋值时,结果和vhdl里用信号赋值一样;

当采用阻塞赋值时,结果和vhdl里用变量赋值一样,功能正确。

Verilog里的阻塞和非阻塞赋值让很多初学者都很纠结,觉得无法理解,个人觉得这对了,连Xilinx的大神们在写文档里的程序的时候

也是随心所欲,会有考虑遗漏的时候,更何况我等初哥

仿真图不小心插进去了,而且重复了,请见谅。

写的有点匆忙,第二段程序有误,修改如下:

process(a)

variable count_r : std_logic_vector(2 downto 0);

begin

count_r := "000";

for i in 0 to 7 loop

if (a(i) = '0') then

count_r := count_r + 1;

end if;

end loop;

count <= count_r;

end process;