谁分析过模块之间在什么情况下可以让输入端连续输入?

时间:10-02

整理:3721RD

点击:

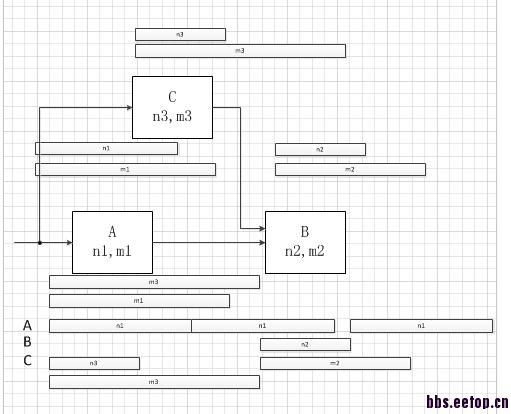

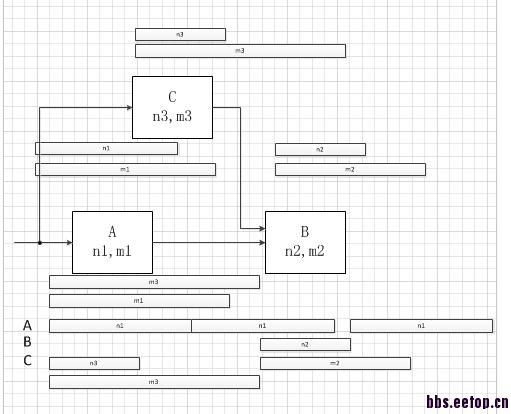

是这么画图分析的码?有没有什么公式可以直接套用?

n的含义是:如果这个模块没有任何外界干扰,一个数据输入该模块后要经过n个时钟周期后才能有新的数据输入这个模块,m不的含义是m个时钟沿后,计算好的数据才会出现在模块的输出端口。

不知道我这样设定两个参数合不合理。

n的含义是:如果这个模块没有任何外界干扰,一个数据输入该模块后要经过n个时钟周期后才能有新的数据输入这个模块,m不的含义是m个时钟沿后,计算好的数据才会出现在模块的输出端口。

不知道我这样设定两个参数合不合理。