qsys使用

时间:10-02

整理:3721RD

点击:

说起来,自己还是挺懒的,quartus还一直停留在7.0版本上,最近看到很多都在用qsys,想着不能太out,于是下了个13.0开始学习,以前用sopc感觉挺好的,真正用了qsys发现太多的不习惯。

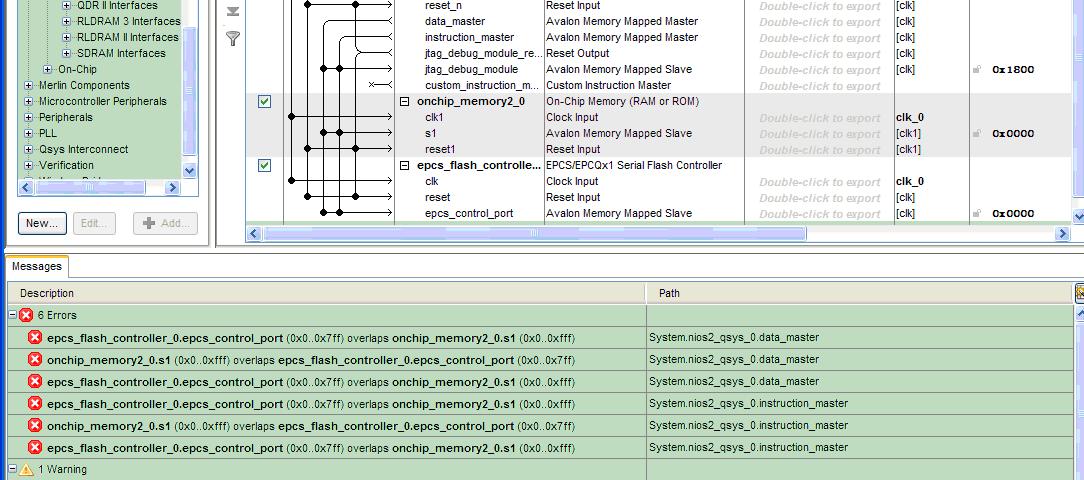

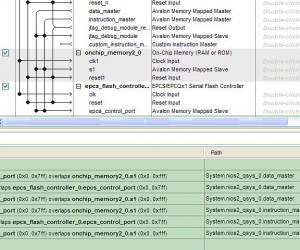

第一次用qsys有点懵,以前sopc都是连好的,不需要自己担心太多,也没进行过深入研究,现在都需要自己连接,网上搜了些帖子,又看了几个例程,马马虎虎的知道哪些重要线该连接,

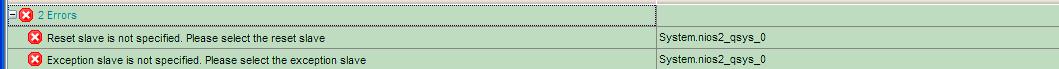

添加了ram后总出现错误

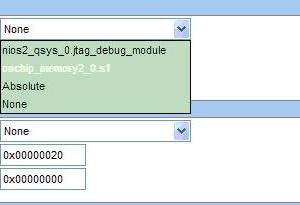

需要在nios cpu上下文章,core Nios II下拉,reset vector和exception vector都需要进行相应的设置,在这里我只是做个简单测试,所以都放在on-chip memory里了

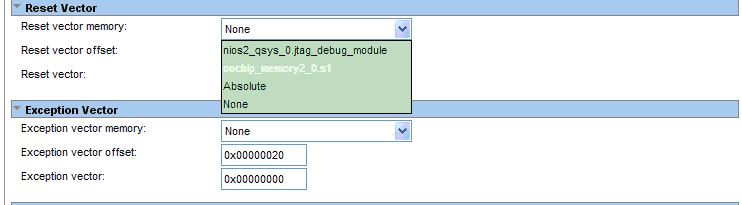

出现如下错误

等所有器件添加完毕,通过system-assign base address消除

另外添加的IP如有conduit的即通过双击变成外部接口

所有IP添加完毕,点击generate生成系统,添加到顶层,进行下一步综合下载。

编译过程又遇到障碍

Error (12006): Node instance "inst" instantiates undefined entity "nios_0824"

qsys不像以前的sopc智能,不知道是我哪里设置不对,还是因为什么原因,需要手动添加生成的.qsys文件到当前工作目录,

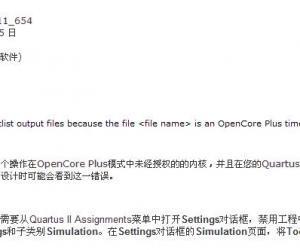

等待编译的过程有点紧张,在最后EDA Netlist Writer的时候又卡住了,

Error (204012): Can't generate netlist output files because the file " F:/FPGA/altera/enet_test/db/ip/tse_test/submodules/altera_tse_crc32galois8.v " is an OpenCore Plus time-limited file

Error (204009): Can't generate netlist output files because the license for encrypted file "F:/FPGA/altera/enet_test/db/ip/tse_test/submodules/altera_tse_crc32galois8.v" is not available

官网上给出了解决方案

按照提示进行了相关设置,再进行编译,总算顺利了。

附件:

器件连接 [发布时间:2014-08-24 19:29:54]

error1 [发布时间:2014-08-24 19:29:54]

cpuset [发布时间:2014-08-24 19:29:54]

altera [发布时间:2014-08-24 19:29:54]

address [发布时间:2014-08-24 19:29:54]

very good

顶,很好

太棒了

请问一下,那如何进行modelsim仿真呢?