full_sync是什么同步机制 急求

input clk1;

input resetn1;

input clk2;

input resetn2;

input set;

output setout;

output set2_reg2;

顶一下

表示没看懂

信息不足,无法分析

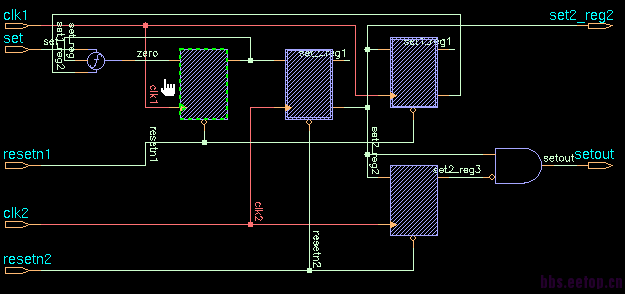

1. 前置逻辑关系是什么?圈起来的F里

2. 寄存器的Q、~Q输出,不清楚

大家看看code吧

module full_sync(

clk1,

resetn1,

clk2,

resetn2,

set, // set signal from clk1 domain

set2_reg2,

setout // set output to clk2 domain

);

input clk1;

input resetn1;

input clk2;

input resetn2;

input set;

output setout;

output set2_reg2;

wire setout;

reg set_reg;

reg set2_reg1;

reg set2_reg2;

reg set2_reg3;

reg set1_reg1;

reg set1_reg2;

wire zero;

assign zero = set | set_reg & ~set1_reg2;

assign setout = set2_reg2 & (~set2_reg3); // output a pulse

always @(posedge clk1 or negedge resetn1)

begin

if(~resetn1)

begin

set_reg <= 1'b0;

end

else

begin

set_reg <= zero;

end

end

// clk2 sync set_reg

always @(posedge clk2 or negedge resetn2)

begin

if(~resetn2)

begin

set2_reg1 <= 1'b0;

set2_reg2 <= 1'b0;

end

else

begin

set2_reg1 <= set_reg;

set2_reg2 <= set2_reg1;

end

end

// clk1 sync set2_reg1

always @(posedge clk1 or negedge resetn1)

begin

if(~resetn1)

begin

set1_reg1 <= 1'b0;

set1_reg2 <= 1'b0;

end

else

begin

set1_reg1 <= set2_reg2;

set1_reg2 <= set1_reg1;

end

end

// clk1 delay set2_reg2

always @(posedge clk2 or negedge resetn2)

begin

if(~resetn2)

begin

set2_reg3 <= 1'b0;

end

else

begin

set2_reg3 <= set2_reg2;

end

end

endmodule

马克一下,代码已出求指导

没有必要这么复杂。2个FF同步,再加一个FF提取上升沿就足够了。

这种写法应该是一个特有写法吧 ,实现特定功能。只是我不知道为啥这么写

也有可能作者一时想多了。这样的电路也不少。

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

xuexiyixia

这个机制的目的是检测set信号由高到低的跳变,在clk2时钟域输出一个clk2 Cycle的高脉冲。要求信号set的高电平宽度不小于clk1 + clk2,否则可能漏脉冲。

牛人啊 谢谢