V6 LVDS串并转换

时间:10-02

整理:3721RD

点击:

各位好,我现在做xilinx V6 与ADC 的LVDS通信,ADC的型号是LTC2175,采用双线,16bit,125MHz采样率;V6内运行的串并转换逻辑会出现尖峰噪声的问题,解串波形也时好时坏(LTC2175的模拟信号输入从示波器上看是好的),请问各位高手是不是我的逻辑时序不够严密?

谢谢!

谢谢!

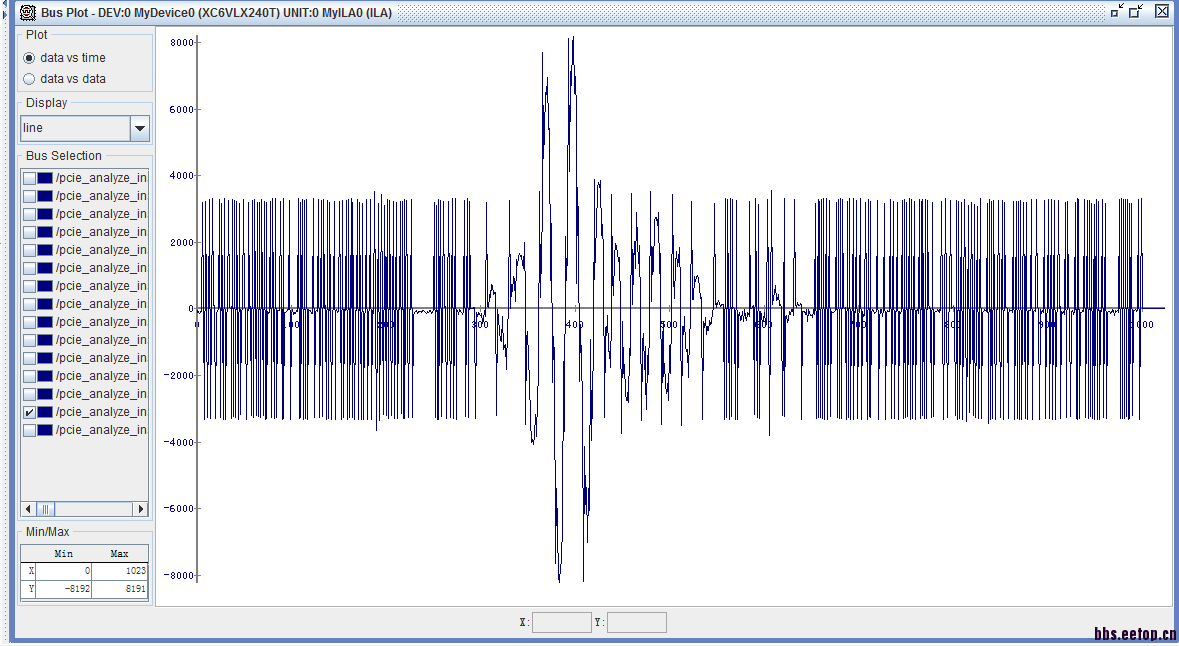

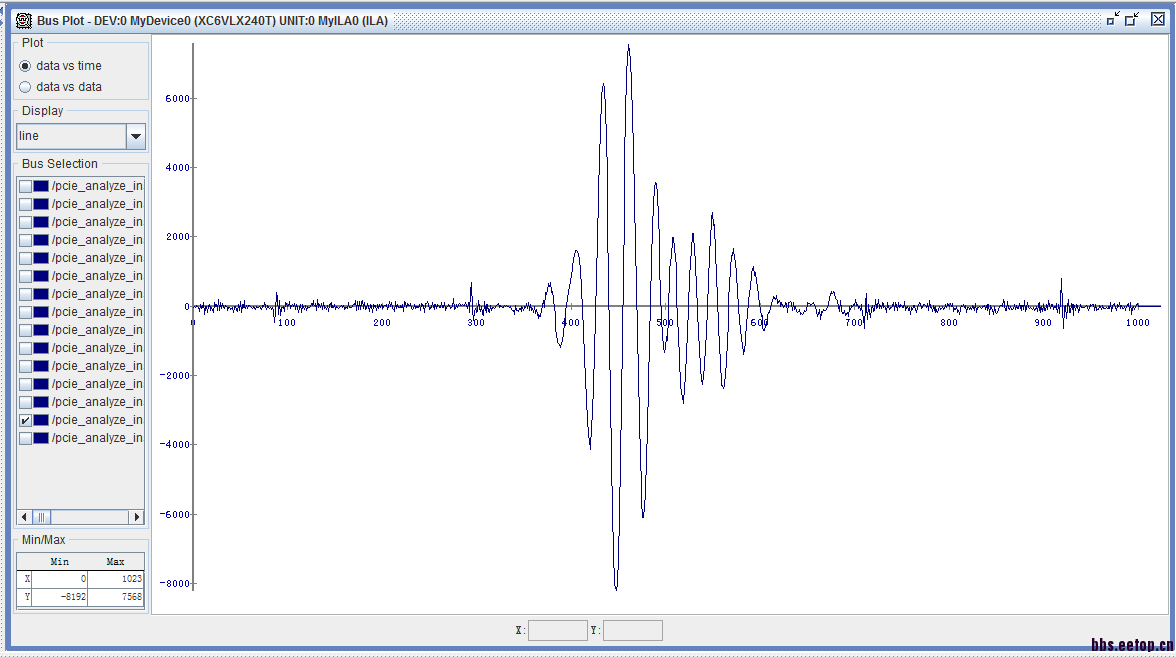

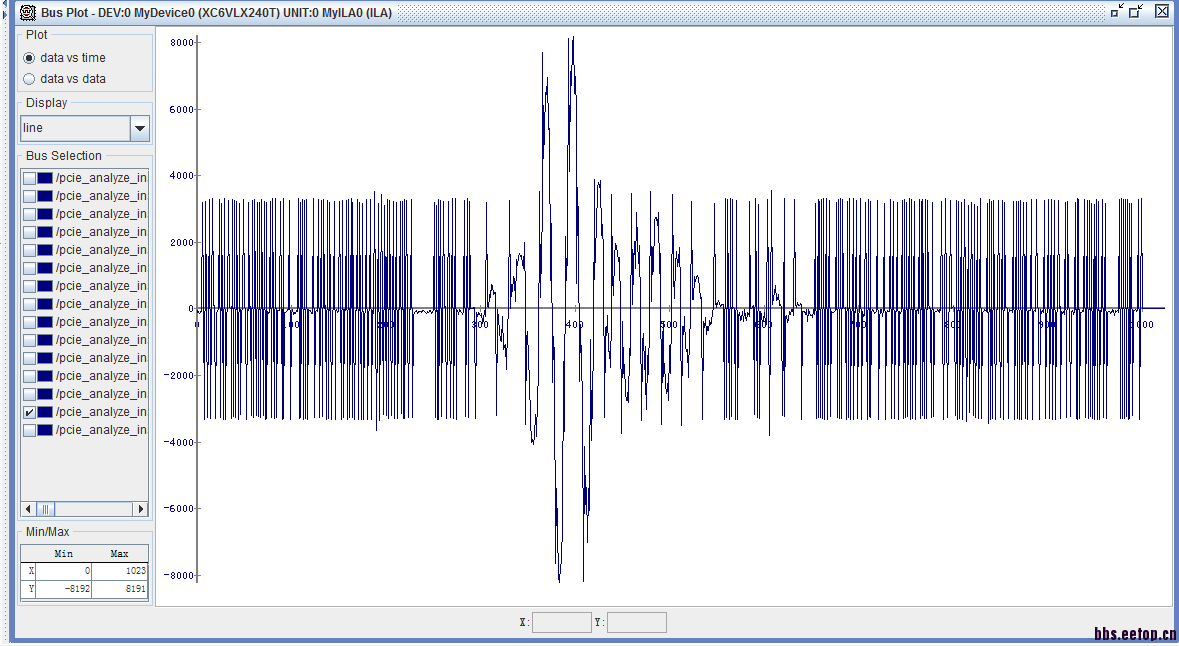

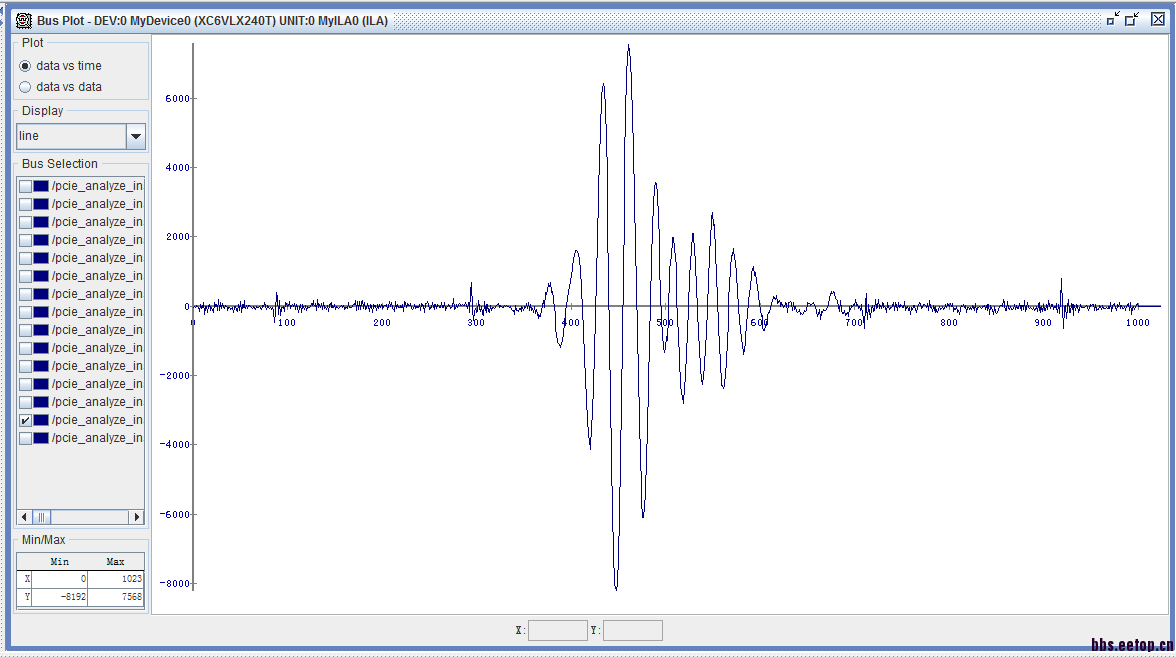

补充一下:第一幅图是存在尖峰的解串波形,第二幅是正常的解串波形,第三幅是示波器显示的进入AD之前的模拟信号。

LVDS的源同步速率是多少? 用的是什么方式去解串的?

您好,LVDS 串行时钟500MHz,DDR模式输出数据,通过IODELAY调整 ISEDERSE接收端的时钟相位对齐,根据帧参数进行一帧数据的调序和寄存。

使用的是泰克的示波器

.。关于尖峰的问题,哥们怎么看?

同步没有做好。

1. 同步 复位端问题 2.CDC抓数端问题

逻辑本身参考的是xapp1071,可能是ISERDESE的输入端,时钟与数据的相位关系不好,毕竟1ns的数据窗口太小,很容易造成时钟边沿的数据采集不正确。

如果是同步问题,那iodelay调整tap后,根据调整方法的不同,可能存在bit的移位,后面iserdes的bitslip可以调整这种移位(就是找字边界),也许能解决你这种问题,尖峰脉冲,很可能是由于数据的高位突然出现了1个或者多个1,也许就是bit移位造成的(猜测)。

如果有训链条件,可以先做LVDS训链,确定好tap和bitslip的值后,再进行AD采集。这个就看现场条件了

感觉是时序不对,要么iodelay,要么mmcm调相

恩恩好的!多谢!