自己写sata控制器遇到的问题,求大神指点~

时间:10-02

整理:3721RD

点击:

物理层没问题,现在传输层是用一个fifo模拟的,在验证链路层时候出现这样的问题:

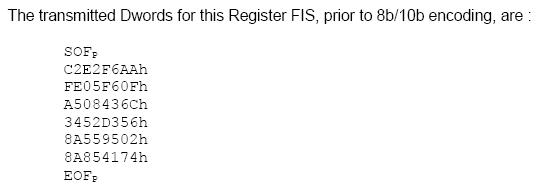

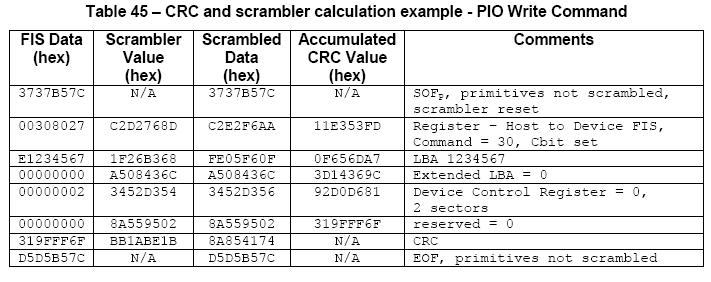

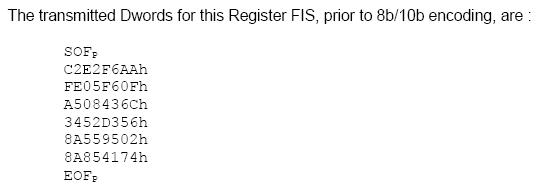

发送数据给sata硬盘,数据时协议里给的那个例子,发送x_rdy...sof,data,crc,eof。

但是每次都是收到r_rdy...r_ip...r_err...

crc和扰码都是和协议里例子一样的,不会有问题,能收到硬盘回应的r_ip,说明发送和接收数据是没问题的,但是为什么总是收到r_err呢?

求解呀。没思路了

发送数据给sata硬盘,数据时协议里给的那个例子,发送x_rdy...sof,data,crc,eof。

但是每次都是收到r_rdy...r_ip...r_err...

crc和扰码都是和协议里例子一样的,不会有问题,能收到硬盘回应的r_ip,说明发送和接收数据是没问题的,但是为什么总是收到r_err呢?

求解呀。没思路了

做好了 说一声

FIS的长度是多少?是命令帧吗?,一般返回RERR一般就是CRC校验错误,如果是PIO data FIS,也可能是帧的长度不符合PIO Setup帧里面的数值

估计得一阵。

是PIO,不算crc的话是20字节,就是图片里的那个FIS

如果发送端到扰码这层都没有错的话就考虑是不是8b-->10b错了,另外看看primitive是不是被正确标记了K,别被认为是data了

8b/10有问题的话,那我发送的x_rdy,sof之类的原语也接收正常呀。

你找个硬盘仿真模型自己仿仿看吧

您说的硬盘仿真模型是什么? 哪里能找到?

是啊,什么叫银盘仿真模型啊

指sata的testbench吧

与硬盘进行数据传输,要求发送数据经过扰码。

学习一下

小编问题解决了吗?