状态机的问题

时间:10-02

整理:3721RD

点击:

用状态机做一个流水灯的实验,希望四个LED可以依次闪烁,当下到片子里面,四个LED全是亮,当我把状态机最后一个状态去掉之后,运行就正常了,我用的是XILINX的XCS250E,是状态机的状态多了之后跑飞吗?

- module fsm_led_4( clk

- ,en

- ,rst

- ,a

- ,b

- ,c

- ,d

- );

-

- parameter FSM_STATES = 7;

- parameter ON = 1'b1;

- parameter OFF = 1'b0;

-

- input clk,en,rst;

- output a,b,c,d;

- wire clk,en,rst;

- wire a,b,c,d;

-

-

- reg [FSM_STATES-1:0] state_current,state_next;

- reg FSM_s1,FSM_s2,FSM_s3,FSM_s4;

- assign a = FSM_s1;

- assign b = FSM_s2;

- assign c = FSM_s3;

- assign d = FSM_s4;

- parameter [FSM_STATES-1 : 0]

- IDLE = 7'b0000001,

- S1 = 7'b0000010,

- S2 = 7'b0000100,

- S3 = 7'b0001000,

- S4 = 7'b0010000,

- S5 = 7'b0100000,

- S6 = 7'b1000000;

-

- always @(posedge clk or posedge rst )

- begin

- if(rst)

- state_current <= IDLE;

- else

- state_current <= state_next;

- end

- always @ (

- state_current

- or en

- )

- begin

- case(state_current)

- IDLE:begin

- if(en)

- state_next <= S1;

- else

- state_next <= IDLE;

- end

- S1:begin

- state_next <= S2;

- end

-

- S2:begin

- state_next <= S3;

- end

-

- S3:begin

- state_next <= S4;

- end

-

- S4:begin

- state_next <= S5;

- end

- S5:begin

- state_next <= S6;

- end

- S6:begin

- if(en)

- state_next <= S1;

- else

- state_next <= IDLE;

- end

- default:begin

- state_next <= IDLE;

- end

- endcase

- end

- always @(state_current)

- begin

- case(state_current)

- IDLE:begin

- FSM_s1 <= OFF;

- FSM_s2 <= OFF;

- FSM_s3 <= OFF;

- FSM_s4 <= OFF;

- end

- S1:begin

- FSM_s1 <= ON;

- FSM_s2 <= OFF;

- FSM_s3 <= OFF;

- FSM_s4 <= OFF;

- end

- S2:begin

- FSM_s1 <= OFF;

- FSM_s2 <= ON;

- FSM_s3 <= OFF;

- FSM_s4 <= OFF;

- end

- S3:begin

- FSM_s1 <= OFF;

- FSM_s2 <= OFF;

- FSM_s3 <= ON;

- FSM_s4 <= OFF;

- end

- S4:begin

- FSM_s1 <= OFF;

- FSM_s2 <= OFF;

- FSM_s3 <= OFF;

- FSM_s4 <= ON;

- end

- S5:begin

- FSM_s1 <= ON;

- FSM_s2 <= ON;

- FSM_s3 <= ON;

- FSM_s4 <= ON;

- end

- S6:begin

- FSM_s1 <= ON;

- FSM_s2 <= ON;

- FSM_s3 <= OFF;

- FSM_s4 <= OFF;

- end

- default:begin

- FSM_s1 <= OFF;

- FSM_s2 <= OFF;

- FSM_s3 <= OFF;

- FSM_s4 <= OFF;

- end

- endcase

- end

- endmodule

仿真过了吗

状态机仿真没问题,奇怪就奇怪在这里。

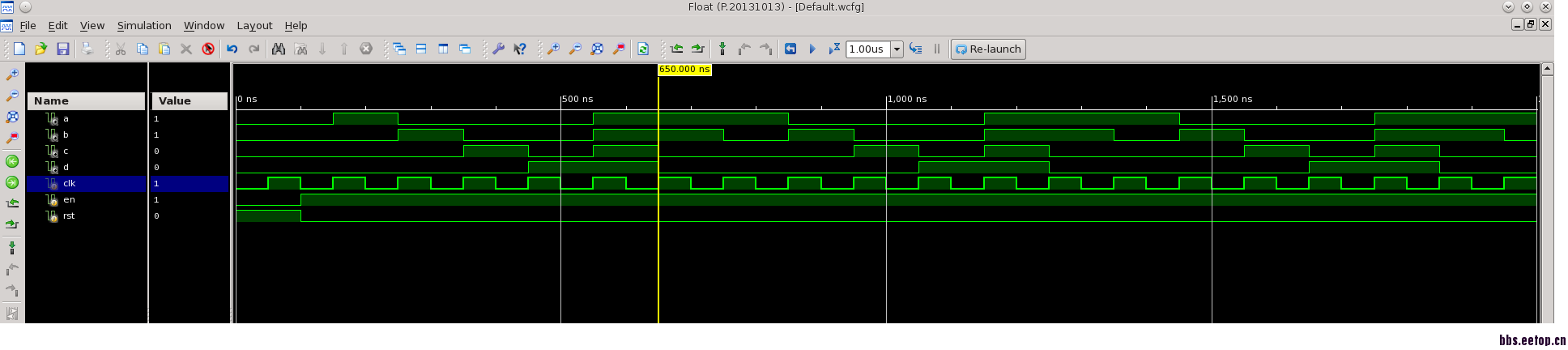

仿真图

你这个clk也太快了把,还有一般三段式状态机组合逻辑部分一般是阻塞赋值

我仿真用的是1MHZ的,实际在片上用的是1hz的频率,能明显看到leds闪烁的刚刚我把IDLE状态去掉了,只保留我需要的那些状态,led闪烁正常了,我在想是不是出入IDLE状态需要给特定的条件,要不然会跑飞

除了那个阻塞赋值没看出别的问题,你的en信号一直为高吗

en 信号是高,我也改成阻塞赋值了,下到板子里状态还是不对,如果没有IDLE状态的话就没有问题,现在只能这样做了。

没道理会这样的啊,你有IDLE状态的时候现象是怎么样的,你输出1的时候LED亮还是输出0的时候LED亮。

状态机好难哦 啊啊

还是感觉比较复杂呀

楚天到了