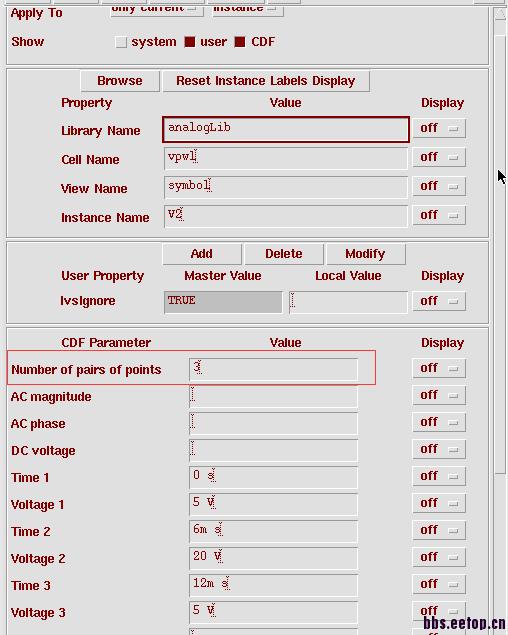

icfb中仿真激励信号vpwl只可以设置50个转折点?

大家好!我需要的时钟信号为“常高--14个上升沿--常高”,使用仿真激励信号vpwl来产生。根据计算值,需要设置58个转折点,即常高2个点+14个上升沿56个点,由于最后一个上升沿后为高,所以不需要设置。可是在设置的过程中发现最多只能设置50个转折点,不知道是我的软件没有破解完全,还是本来就只能设置50个点。如果是后者,我应该如何产生这样的时钟信号呢?谢谢~

另外,vpwlf可以选择file输入,请问有谁知道该file是什么格式,请不吝赐教!提供user guide也非常感谢!

在网上搜索了一下,vpwl默认只能设置50个转折点,可以通过修改vpwl.cdf文件来增加,具体怎么操作,有谁知道吗?

file格式的问题已经解决,如要产生0~100ns为高电平,100~160ns之间为2个上升沿,占空比为50%,160ns以后为高电平,假设高电平为3V,则file的写法为:

第一种:000e-9 3

100e-9 3

101e-9 0

120e-9 0

121e-9 3

140e-9 3

141e-9 0

160e-9 0

161e-9 3

第二种:0.000000000 3

0.000000100 3

0.000000101 0

0.000000120 0

0.000000121 3

0.000000140 3

0.000000141 0

0.000000160 0

0.000000161 3

第三种:0.00e-7 3

1.00e-7 3

1.01e-7 0

1.20e-7 0

1.21e-7 3

1.40e-7 3

1.41e-7 0

1.60e-7 0

1.61e-7 3

左边一列为时间,单位为‘S’;右边一列为幅值,单位为'V',都不能写单位,且不能用变量名。

CIW->Tools->CDF->Edit,选中vpwl,

仔细看看vpwl的t1,v1的属性,按照那个添加t51,v51……,t58,v58试试看看行不行。

谢谢!我尝试用您的方法,Tools->CDF->Edit->AnalogLib->vpwl->这个时候,我该怎么继续操作呢?

注意右上角的CDF Type选Base,这里面的Component Parameters里就有了t1,v1之类的,点Edit,在Choose Parameter里面选中t1,就能看到t1的一些定义方法了。然后将CDF Type选回User,按照类似的写法添加自己的t51,v51之类的,如果Base里面你有权限更改的话,你在Base里面添加也行,也可以在Specify里面添加。试一下吧,只能说,这样可能行。没试过的说。

请问vpwlf中的信号文件,应该是什么格式的和应该放在哪里。

为什么我一打开默认是2个?如何让它变多啊