FPGA高速串并:BUFIO2驱动多个ISERDES问题

时间:10-02

整理:3721RD

点击:

各位大侠:背景情况:

目前我有一个设计需求,外部输入同步时钟一对LVDS,与其同步的16位数据LVDS,共17个差分对输入,使用时钟对16位数据进行采集接收,时钟最高输入频率500MHz,SDR模式。

同一个片子有两个相同的采集通道,因此共2对时钟,32对数据,分别采集。

我的考虑:

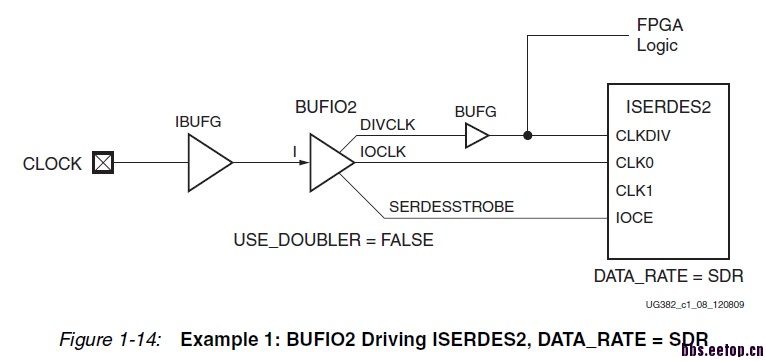

由于使用了低成本的spartan6 lx100t芯片,外部输入可能运行的最高频率约为200MHz,因此需要将每位数据使用ISERDES进行1:4的串并转换,这样片内使用64bitsFIFO接收,可将内部时钟频率降到125MHz。

问题:

1,FPGA的BUFIO2资源数量是有限的,使用一个BUFIO2驱动所有的16个ISERDES2,由于这16位不在同一个BANK上,更不在同半个BANK上(好像一个BUFIO2只能对应半个BANK),就需要多个BUFIO2去分组驱动不同半BANK上的ISERDES2,这样就得明确硬件上哪些数据位对应的是哪个BUFIO2,这个从哪里获得信息?

2,是否可以把片内的32个BUFIO2全部用上,由于管脚只使用了BANK0和BANK1,而BUFIO2是分布在所有的bank上,按表面理解其他BANK的BUFIO2是不能驱动BANK0和BANK1的ISERDES2的,有没有可能?

3,目前我尝试上述1中的方式,报错:ERRORlace:1318 - User has over-constrained component BUFIO2_Iinst. There are

no placeable sites that satisfy the user constraints. Please review the user

constraints on the driver component and the load components of BUFIO2_Iinst.

请高手指出问题所在或者另辟蹊径解决这个应用,谢谢。

目前我有一个设计需求,外部输入同步时钟一对LVDS,与其同步的16位数据LVDS,共17个差分对输入,使用时钟对16位数据进行采集接收,时钟最高输入频率500MHz,SDR模式。

同一个片子有两个相同的采集通道,因此共2对时钟,32对数据,分别采集。

我的考虑:

由于使用了低成本的spartan6 lx100t芯片,外部输入可能运行的最高频率约为200MHz,因此需要将每位数据使用ISERDES进行1:4的串并转换,这样片内使用64bitsFIFO接收,可将内部时钟频率降到125MHz。

问题:

1,FPGA的BUFIO2资源数量是有限的,使用一个BUFIO2驱动所有的16个ISERDES2,由于这16位不在同一个BANK上,更不在同半个BANK上(好像一个BUFIO2只能对应半个BANK),就需要多个BUFIO2去分组驱动不同半BANK上的ISERDES2,这样就得明确硬件上哪些数据位对应的是哪个BUFIO2,这个从哪里获得信息?

2,是否可以把片内的32个BUFIO2全部用上,由于管脚只使用了BANK0和BANK1,而BUFIO2是分布在所有的bank上,按表面理解其他BANK的BUFIO2是不能驱动BANK0和BANK1的ISERDES2的,有没有可能?

3,目前我尝试上述1中的方式,报错:ERRORlace:1318 - User has over-constrained component BUFIO2_Iinst. There are

no placeable sites that satisfy the user constraints. Please review the user

constraints on the driver component and the load components of BUFIO2_Iinst.

请高手指出问题所在或者另辟蹊径解决这个应用,谢谢。

我也想关注这个问题。请高人指点。

不会。路过

持续关注

不应该就这么沉了吧?

由于使用了低成本的spartan6 lx100t芯片,外部输入可能运行的最高频率约为200MHz,因此需要将每位数据使用ISERDES进行1:4的串并转换,这样片内使用64bitsFIFO接收,可将内部时钟频率降到125MHz。