ARM中MMU问题

时间:10-02

整理:3721RD

点击:

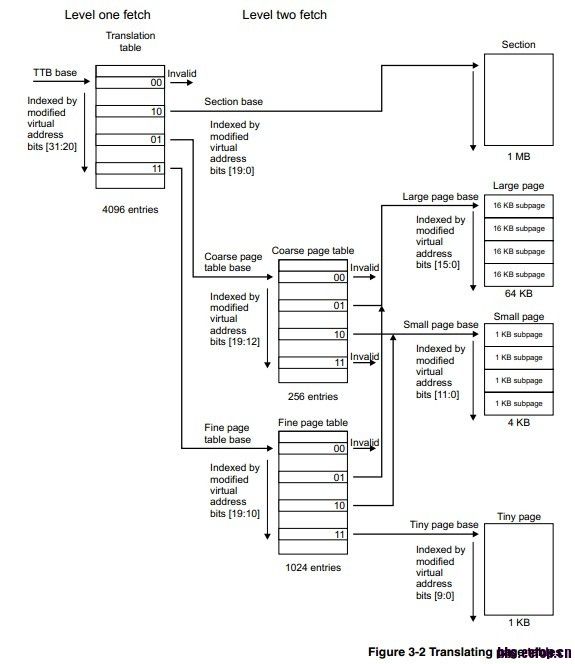

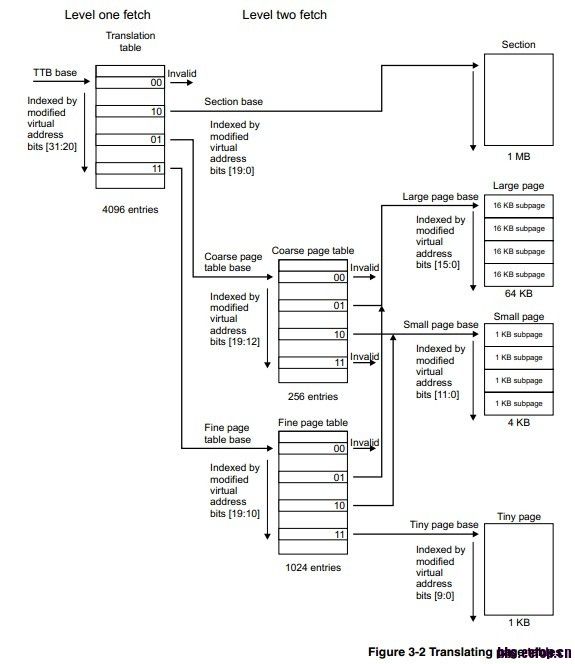

请教一下,为什么ARM中的MMU在进行页表搜索(TTW)的时候,要分两步进行呢?它的页表为什么要这样划分,为什么不一步查询呢?谢谢!

最主要的原因就是工艺达不到,超短的时间内完成批量查表是很困难的

就好比我们为什么要把一条指令的操作过程分 IF ,ID,EX,MEM,WB ,如果工艺好,也完全可以在不降低clk的频率的情况下把5个操作放一个clk里执行,实际上目前还达不到这么能力

我感觉不是这个原因吧,我看网上说是页表大小的问题,不过我也搞不懂...

你给的图应该是 带历史页表的2位分支预测,第一级是先预测一个结果,如果预测是有分支,第二级再查表输出一个结果.

哦 这样哦 谢谢你~

我觉得也还不是这个。一楼说的工艺和速度我觉得如果是放置在片内的部分的话,倒还真有这么一点考虑的。因为一个RAM的深度不能太大。

我认为最主要的是,出于资源考虑,让一个表的entry不要太大。

举一个例子:

假设,按照你说的用一级查表实现,那么对于32bit的地址索引,要求页表大小能支持最小页为1KB,需要的entry数目是多少呢?答案:4GB÷1KB = 4M,这个太多了,深度太多,查找也受限制。实际上系统的需求一般是,有一部分的页1KB,有一部分的4KB,有些64KB,有些1MB。因此,合理的做法就是分多级表,将页大小相同的放置在同一个表里面。

X86-64采用64bit寻址,如果按照一级索引,是不可能实现的。因此,X86里面是按照每8bit成为一级,进行了N次寻址之后得到最终的页。

学习了 非常谢谢你!

学习下

应该是页表大小限制,一个页表的大小不能夸一个内存页面。