C8051F120+CY7C68013A输出数据正常输入数据全是0

时间:10-02

整理:3721RD

点击:

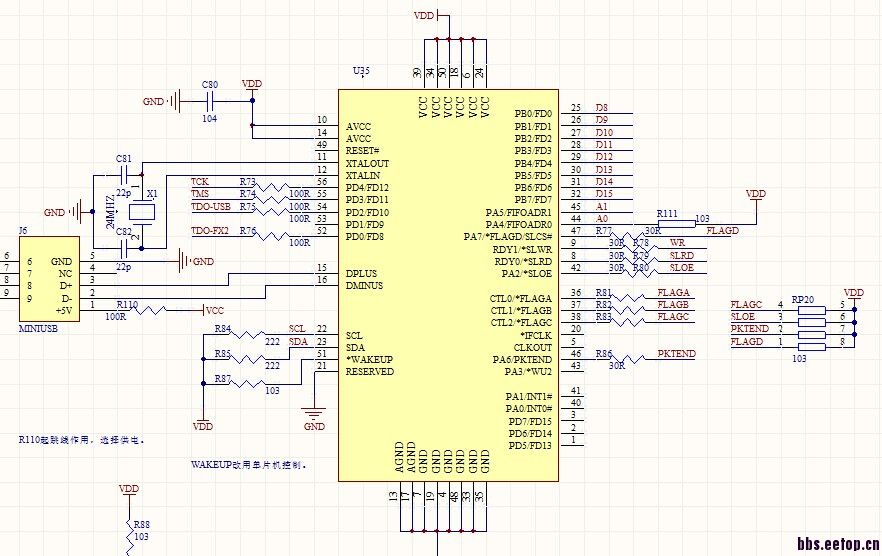

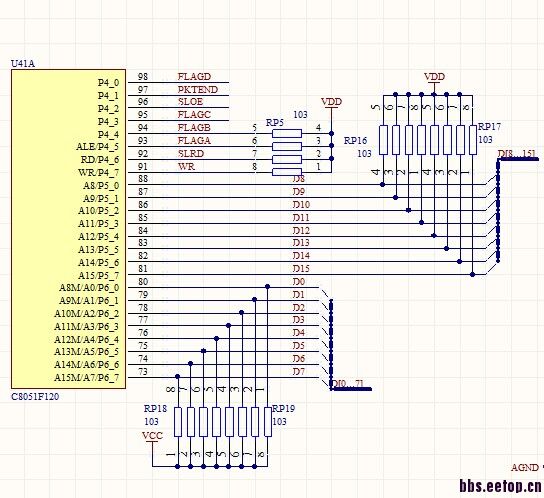

C8051F120+CY7C68013A,遇到的问题是从计算机输出数据到单片机的时候正常,从单片机输出数据到计算机的时候不正常,数据全为0。表现为单片机无法拉高数据总线,但是当把USB的数据总线脚挑起来之后,数据线的信号能改变了。这说明USB芯片这端始终把单片机引脚拉低了。但是在总线中间接个245总线芯片,其他信号不变,之后就能正常使用,IN正常OUT也正常。现在感觉可能出现的问题是:1,USB芯片本身有缺陷,同时买的两片,都有类似问题,其他批次的以前买的也有类似问题,所以这个不太成立;2,配置问题,也就是在初始化的是时候没有配置好,但是问题在哪里没有找到;3,在IN和OUT方向通过A0A1切换时,USB芯片应该自动切换总线方向,所以第二点可能 不会有结果。现在该问题还没解决,请各位大侠帮帮忙看看。

初始化代码如下:

void TD_Init(void) // Called once at startup

{

// set the CPU clock to 48MHz

CPUCS = ((CPUCS & ~bmCLKSPD) | bmCLKSPD1) ;

// set the slave FIFO interface to 48MHz

IFCONFIG = 0xcb;

REVCTL=0x03; // REVCTL.0 and REVCTL.1 to set to 1

SYNCDELAY;

SYNCDELAY; // see TRM section 15.14

EP2CFG = 0xA2;

SYNCDELAY;

EP4CFG = 0xA0;

SYNCDELAY;

EP6CFG = 0xE2;

SYNCDELAY;

EP8CFG = 0xE0;

SYNCDELAY;

FIFORESET = 0x80; // activate NAK-ALL to avoid race conditions

SYNCDELAY; // see TRM section 15.14

FIFORESET = 0x02; // reset, FIFO 2

SYNCDELAY; //

FIFORESET = 0x04; // reset, FIFO 4

SYNCDELAY; //

FIFORESET = 0x06; // reset, FIFO 6

SYNCDELAY; //

FIFORESET = 0x08; // reset, FIFO 8

SYNCDELAY; //

FIFORESET = 0x00; // deactivate NAK-ALL

SYNCDELAY;

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY; //

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY;

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY; //

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY;

// out endpoints do not come up armed

// since the defaults are double buffered we must write dummy byte counts twice

SYNCDELAY;

EP2BCL = 0x80; // arm EP2OUT by writing byte count w/skip.

SYNCDELAY;

EP2BCL = 0x80;

SYNCDELAY;

// since the defaults are double buffered we must write dummy byte counts twice

SYNCDELAY;

EP2BCL = 0x80; // arm EP2OUT by writing byte count w/skip.

SYNCDELAY;

EP2BCL = 0x80;

SYNCDELAY;

EP4BCL = 0x80; // arm EP4OUT by writing byte count w/skip.

SYNCDELAY;

EP4BCL = 0x80;

SYNCDELAY;

//EP6BCL = 0x80; // arm EP4OUT by writing byte count w/skip.

SYNCDELAY;

// EP6BCL = 0x80;

SYNCDELAY;

PINFLAGSAB = 0xc8; //FLAGB->EP2 FF ,FLAGA->EP2 EF。0时是空,1时是非空

SYNCDELAY;

PINFLAGSCD = 0xEA; //FLAGD->EP6 FF,,\FLAGC->EP6 EF,

PORTACFG |= 0X80;

SYNCDELAY;

PORTACFG |= 0X40;

EP2FIFOCFG = 0x14; //AUTOOUT=1, WORDWIDE=0,8bits

SYNCDELAY;

EP2FIFOCFG = 0x14; //AUTOOUT=1, WORDWIDE=0,8bits

SYNCDELAY;

EP4FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

EP4FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

FIFOPINPOLAR = 0x00; // all signals active low

SYNCDELAY;

EP6FIFOCFG = 0x4C; //AUTOIN=1, WORDWIDE=0,8bits

SYNCDELAY;

EP6FIFOCFG = 0x4C; //AUTOIN=1, WORDWIDE=0,8bits

SYNCDELAY;

EP8FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

EP8FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

}

初始化代码如下:

void TD_Init(void) // Called once at startup

{

// set the CPU clock to 48MHz

CPUCS = ((CPUCS & ~bmCLKSPD) | bmCLKSPD1) ;

// set the slave FIFO interface to 48MHz

IFCONFIG = 0xcb;

REVCTL=0x03; // REVCTL.0 and REVCTL.1 to set to 1

SYNCDELAY;

SYNCDELAY; // see TRM section 15.14

EP2CFG = 0xA2;

SYNCDELAY;

EP4CFG = 0xA0;

SYNCDELAY;

EP6CFG = 0xE2;

SYNCDELAY;

EP8CFG = 0xE0;

SYNCDELAY;

FIFORESET = 0x80; // activate NAK-ALL to avoid race conditions

SYNCDELAY; // see TRM section 15.14

FIFORESET = 0x02; // reset, FIFO 2

SYNCDELAY; //

FIFORESET = 0x04; // reset, FIFO 4

SYNCDELAY; //

FIFORESET = 0x06; // reset, FIFO 6

SYNCDELAY; //

FIFORESET = 0x08; // reset, FIFO 8

SYNCDELAY; //

FIFORESET = 0x00; // deactivate NAK-ALL

SYNCDELAY;

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY; //

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY;

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY; //

OUTPKTEND = 0x82; // Arm both EP2 buffers to “prime th

SYNCDELAY;

// out endpoints do not come up armed

// since the defaults are double buffered we must write dummy byte counts twice

SYNCDELAY;

EP2BCL = 0x80; // arm EP2OUT by writing byte count w/skip.

SYNCDELAY;

EP2BCL = 0x80;

SYNCDELAY;

// since the defaults are double buffered we must write dummy byte counts twice

SYNCDELAY;

EP2BCL = 0x80; // arm EP2OUT by writing byte count w/skip.

SYNCDELAY;

EP2BCL = 0x80;

SYNCDELAY;

EP4BCL = 0x80; // arm EP4OUT by writing byte count w/skip.

SYNCDELAY;

EP4BCL = 0x80;

SYNCDELAY;

//EP6BCL = 0x80; // arm EP4OUT by writing byte count w/skip.

SYNCDELAY;

// EP6BCL = 0x80;

SYNCDELAY;

PINFLAGSAB = 0xc8; //FLAGB->EP2 FF ,FLAGA->EP2 EF。0时是空,1时是非空

SYNCDELAY;

PINFLAGSCD = 0xEA; //FLAGD->EP6 FF,,\FLAGC->EP6 EF,

PORTACFG |= 0X80;

SYNCDELAY;

PORTACFG |= 0X40;

EP2FIFOCFG = 0x14; //AUTOOUT=1, WORDWIDE=0,8bits

SYNCDELAY;

EP2FIFOCFG = 0x14; //AUTOOUT=1, WORDWIDE=0,8bits

SYNCDELAY;

EP4FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

EP4FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

FIFOPINPOLAR = 0x00; // all signals active low

SYNCDELAY;

EP6FIFOCFG = 0x4C; //AUTOIN=1, WORDWIDE=0,8bits

SYNCDELAY;

EP6FIFOCFG = 0x4C; //AUTOIN=1, WORDWIDE=0,8bits

SYNCDELAY;

EP8FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

EP8FIFOCFG = 0x04; //AUTOOUT=0, WORDWIDE=0,8bits

SYNCDELAY;

}

USB芯片端口配置有三种状态,一种开漏,一种三态,一种准双向。若果没配置好,就会出现你的描述。