诚心求教一个用延时的时钟采样的设计

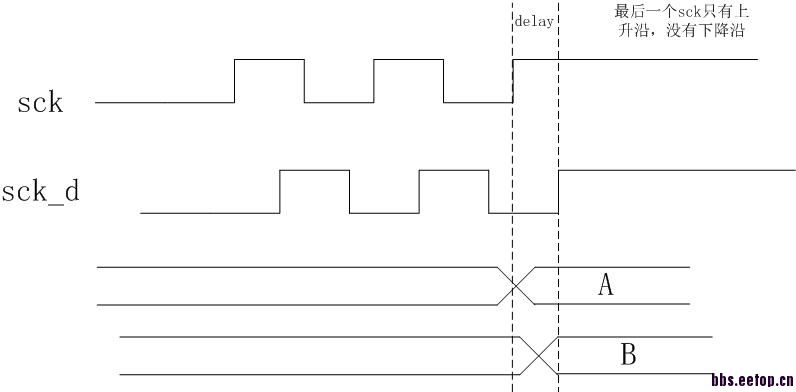

我做的项目里有这么一处特殊的设计,有一个spi端口的输入时钟sck,将这个sck延时了若干ns产生出了sck_d,用sck触发产生了信号A,A经过了一个组合逻辑产生信号B,这个信号B需要被sck_d相对于sck的同一个沿采样,想请教各位后端高手:

1.这个时钟的延时应该怎么实现呢?我尝试写了很多inverter,但综合时貌似被优化掉了

2.在做综合和STA时,应该怎么设置来检查timing,保证A经过组合逻辑后能被sck_d准确采样呢?或者说工具能不能检查这种特殊的采样呢

这个问题困扰我很久了,诚心求教,感激涕零!下图为该设计的时序图

在可约束设计中,是禁止这么去设计电路的

这里,有一个关键时钟sck_d,在约束文件里是很难被准确创建的,它相对于sck的相位延迟存在很大的不确定性

建议使用sck的上升沿产生信号A,然后再使用sck的下降沿去采用其逻辑输出

谢谢大神的回答!是这样的,那个sck的最后一拍是只有上升沿,没有下降沿的,所以只能用sck的delay来采样数据。

看了您的回复,觉得可能是没法通过工具来检查了。我打算在做STA的时候,把sck和sck_d设为false_path。然后在做CTS的时候,在sck和sck_d间插入尽可能多的buffer,您看这样可行吗?

这些东西用数字逻辑实现很不稳定,不建议使用。

如果你非要这么设计,在门级网表后期处理是可以的

但是针对工艺的影响,建议留有更大的延迟余量,在sck和sck_d之间,进而提高产品良率

不过作为一名严谨的研发人员,你这种设计方法不提倡

结合我个人的经验,应该是存在别的方式,能够达到你的要求的,你不妨再仔细考虑一下

多谢耐心的回答。该设计从纯逻辑角度来讲,确实很难有更好的办法。但我觉得您说的很对,用数字后端的方式去调节那个延时,确实存在不确定性。我在考虑将sck通过数字端口引出来,用模拟电路的方式去实现这个延时,然后再通过端口引回数字电路部分,不知这样是否能够更加可控?

谢谢!

有一个折中的方法:

比如,使用STDCell组合几组延迟单元,然后串联起来,同时设置一个选择端口,通过软配置可以选择多种组合

使用这种结构去控制sck和sck_d的相位关系,有两种好处:

1. 便于配置合适的相位关系;2. 便于加速测试;3. 缺点就是可能存在较多的冗余单元

还有一种特定方式:

如果该设计的有且只有一条路径,或者存在明显的关键路径,可以使用该路径作为参考路径。使用同样的单元,再增加一定的延迟单元作为sck->sck_d的传播路径。好处就是相位关系控制的较为准确,缺点就是实用面窄,并且需要分析关键路径(门级网表)

我觉得您提供的第一种方法非常好,增加了调试的灵活性,打算尝试一下。还想请教一下,我如果直接在rtl中调用工艺库里的standard cell,比如串联10个inverter,做综合的时候应该不会被优化掉的吧?

你用的是FPGA吗?可以用DCM产生新的时钟sck_d,而且XILINX的FPGA还有IODELAY单元用来延时

如果功能满足的话,为何不用异步FIFO,简单粗暴的解决问题。如果不能用,那么设置clk_d为generated clock from clk,这样工具应该能分析到FLOP B的时序是否满足吧。

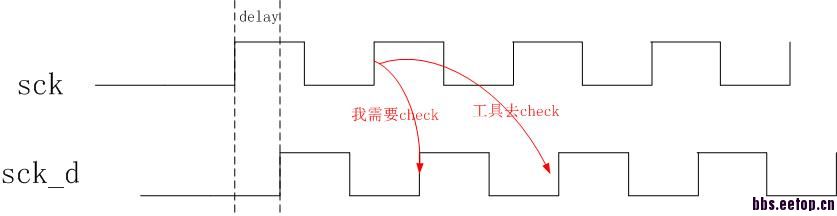

异步fifo不可行,因为spi送数据时,为了低功耗系统主clk还没有启动,所有只能拿sck去采样数据,但可恶就是sck的最后一拍没有下降沿。将sck_d设为sck的generate clk我想过了啊,但sck打出的数据估计工具会在sck_d的下一个沿才会去check timing吧,我需要的是相对于sck的同一个沿。

如图所示:

1. 我理解你是有两个clk的,第一个sck,第二个sck_d,sck打出的data A,并generate 出来data B,然后用sck_d去sample。如果不是非得要求一个时钟内采样,可以用异步fifo,如果非要求一个时钟内,这就不可行了。 2. 关于generated clk是否将数据在当前cycle还是下一个cycle来分析,你可以试一下,看实际上出来的时序报告分析哪个周期。试想一下,很多正常的设计本身就会把sck作为输入时钟,送到PLL或者FPGA的DCM里面,然后产生时钟来sample输入的data,如果工具分析下一个cycle的话,那么工具岂不是会有问题? 另,我不是做后端的,所以意见仅供参考。

set_dont_touch就可以了

1还是不太可行。2觉得可以尝试一下,看看到底工具是怎么check的。

得到大家的帮助,思路果然清晰了很多,多谢回答!

根据描述,其实就是需要产生一个相位差为X的时钟

可以把时钟sck输入给DCM或者PLL,配置相应的输出时钟相位即可

不建议用组合逻辑搭建延时电路,FPGA内部的延时一般通过时钟实现,你的时钟频率越高,可控的延时精度就越大

fifo不错的方法

不知道是用FPGA还是做IC。

FPGA的话,如果是x家的,用iodelay来解决这个问题。

你的spi有片选信号CS_n吗?

如果有的话,我感觉你的sck_d的功能可以用CS_n的上升沿来代替。

一般来说,CS_n是在最后一个sck之后,原本应该来下降沿的地方上升的。

教你一个简单有效的方法,压箱底传男不传女。

在FPGA或CPLD连上两个脚,一个输出一个输入,输出等于SCK,输入就是SCK_D,这样就能保证时延至少一个gate to gate delay。