Xilinx的时钟资源中的BUFGIO2和BUFG有什么区别啊?

时间:10-02

整理:3721RD

点击:

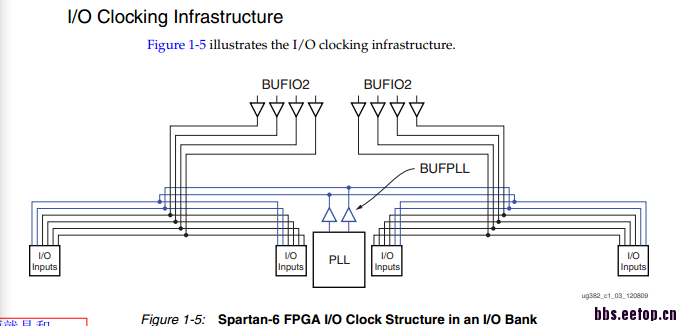

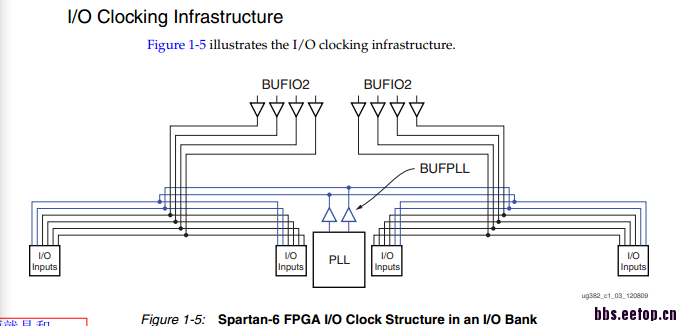

是不是BUFGIO2的时钟偏移比BUFG更小?

还有,图中的那个PLL是不是离管脚很近的位置?(这样延迟小一点)

还有,图中的那个PLL是不是离管脚很近的位置?(这样延迟小一点)

我知道的是BUFIO只能驱动到IO Bank里的时钟资源,驱动不了FPGA里的logic resource,如CLB等

BUFG则是驱动全局时钟网

BUFIO2只能驱动IO

BUFGIO在FPGA上是不是也表现为一个时钟网络?

我想知道BUFG算是“缓冲”还是“网络”,它在FPGA上表现为什么?

我这样理解对不对?BUFG和其他的CLB一样,在FPGA上也表现为一个有输入端口和输出端口的实例,然后这个实例的输出端口直接和时钟网络相连。

又多學到一些東西

BUFG和BUFIO都是时钟缓冲器,输入端是时钟,输出端是时钟网络,它们在FPGA里表现为原语(primitive),说实例有些不准确

比如说有一个时钟从 “全局时钟端口”GCLK进来,然后FPGA是怎么把这个端口路由到BUFG的输入端的呢?是不是这段连线是随便怎么路由的?(我说的是从FPGA端口到BUFG输入端那一段网线),还有呀,为什么时钟信号要经过一个时钟缓冲器,是不是增加带负载能力?

,还有呀,BUFG的延迟和BUGIO2的延迟一样吗?我没有在文档里看到相应内容啊

不胜感激!

你问的太深了,回答不了

驱动能力有区别。