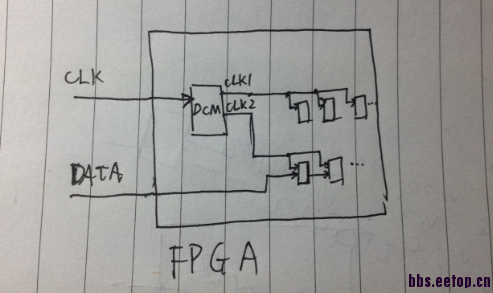

像这张图怎么加偏移约束?加了之后会有什么效果?

时间:10-02

整理:3721RD

点击:

之前都是一个时钟,现在的话时钟经过了DCM产生了两个时钟clk1和clk2,clk1还是原来的样子,clk2的话是clk1的8倍频,我的目的是:clk2这个时钟没经过8个时钟沿打入一次DATA,那么我该怎么写偏移约束呢,是不是还是和原来一样(就是仅仅规定CLK和DATA的相位关系,然后软件总动帮我打成目的?)

之前都是一个时钟,现在的话时钟经过了DCM产生了两个时钟clk1和clk2,clk1还是原来的样子,clk2的话是clk1的8倍频,我的目的是:clk2这个时钟没经过8个时钟沿打入一次DATA,那么我该怎么写偏移约束呢,是不是还是和原来一样(就是仅仅规定CLK和DATA的相位关系,然后软件总动帮我打成目的?)(问:偏移约束的目的是不是这样:如果针对CLK和DATA加偏移约束,综合后就能保证“所有与CLK有关的寄存器(包括受CLK派生时钟的寄存器)”都能在其所属时钟下正确打入数据,而不会出现亚稳态的状况)

你后边说的是对的,只要你给出了data和CLK和关系,然后给出dcm的约束,至于CLK2和data的关系是分析工具自己分析的,你只需要查看时序报告就好了。

有几个问题啊:1,什么叫“给定DCM的约束”。

2,现在的情况是clk1就是原时钟clk,那么如果把DATA接到上面一排寄存器的话,添加偏移约束的情形和通常情况应该是一样的。

但是现在DATA接到了下面一排寄存器(由clk2控制),而clk2的频率是clk1的8倍(相位则没有变化)。这个时候工具在分析偏移约束的时候是怎么做的呢?