关于verilog数字系统设计教程(2版 夏宇闻)书中的一个问题

时间:10-02

整理:3721RD

点击:

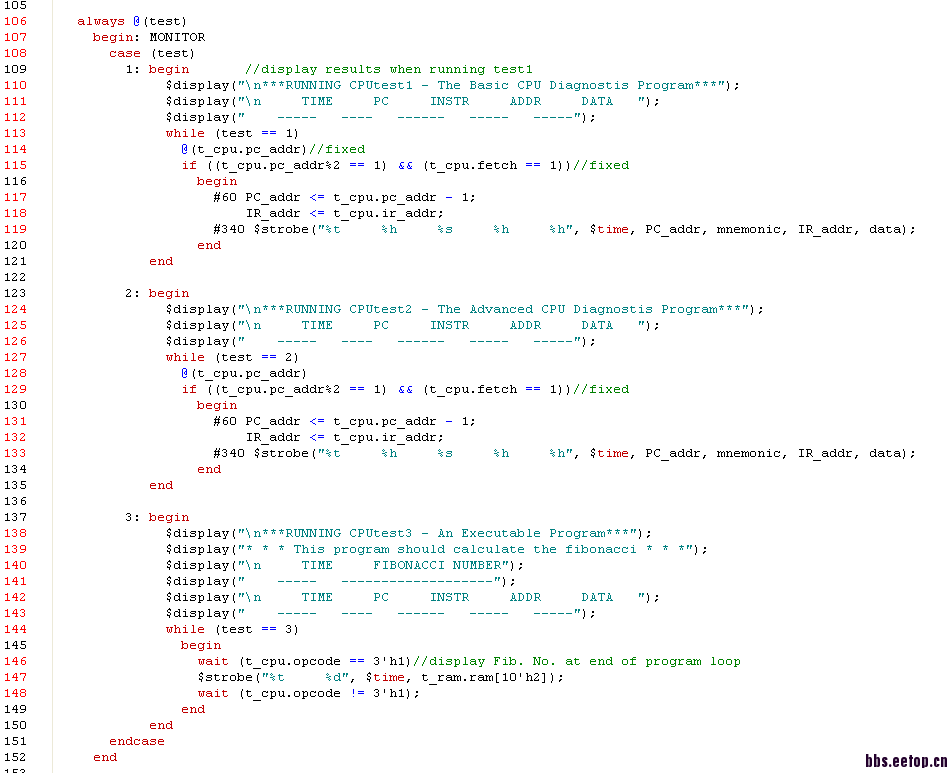

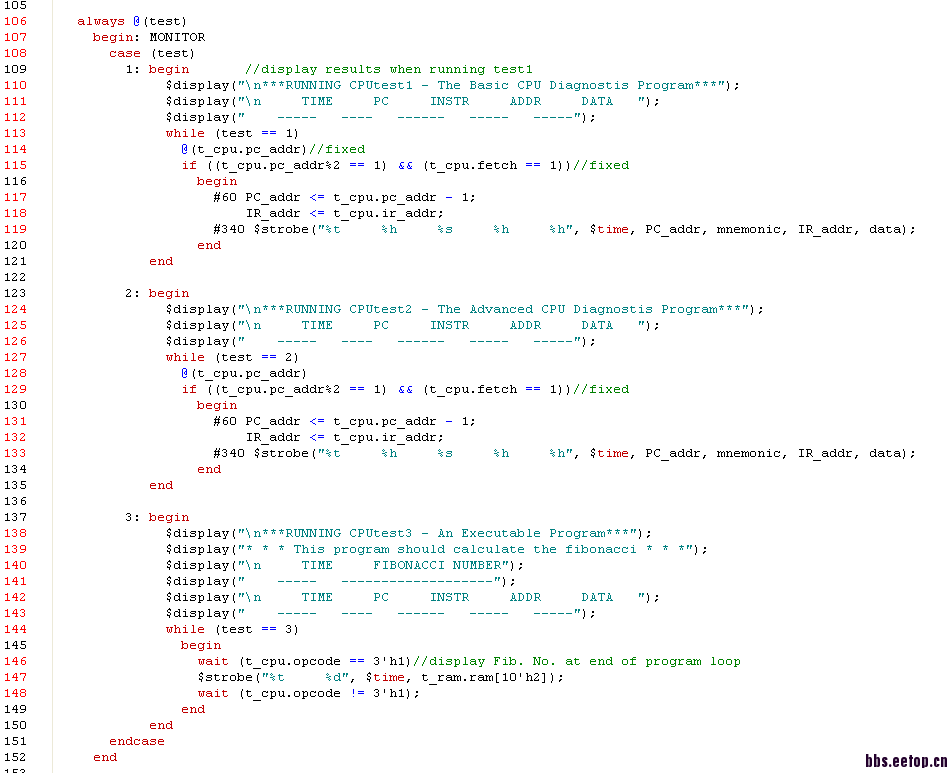

【1】书中第17章RISC_CPU中,page274,在cputop中有一部分不太理解。

【2】page269,关于RAM和ROM大小的问题,感觉不太对,按照地址译码器的代码写法,RAM大小应该是11‘'7ff,不应该是10'h3ff,ROM大小应该是13'h17ff,不应该是13'h1fff。

为什么要判断对t_cpu.pc_addr是否被2除余1?以及#60 #140。

另外,书中page264状态机的代码中,为何是在clk负沿响应呢?

【2】page269,关于RAM和ROM大小的问题,感觉不太对,按照地址译码器的代码写法,RAM大小应该是11‘'7ff,不应该是10'h3ff,ROM大小应该是13'h17ff,不应该是13'h1fff。

第二个问题,地址译码只是说它能识别这么多的地址,至于用多少,看你吧,所以ram定义3ff深度是问题的。ROM定义成1FFF应该是为了方便处理吧,因为这里ram和rom用的是同一根地址线,这点page273可以看到。

第一个不明白你有什么问题

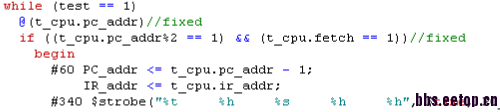

谢谢你的回答! 第二个问题,RAM定义为3ff,是小于7ff的,所以没问题,认同。但是ROM定义的范围大于了17ff,达到1fff,这样在寻址的时候,如果{addr[12],addr[11]}=2'b11的时候就认为是寻址RAM了,不会出现问题吗? 第一个问题我没有叙述好。我不理解的是代码中的此处:

为什么要判断对t_cpu.pc_addr是否被2除余1?以及#60 #140。

另外,书中page264状态机的代码中,为何是在clk负沿响应呢?

给自己顶一下。

图中语句只为了确定每一条指令的首地址(没一条指令由两字节)pc_addr;#60#340之后的位置为alu输出发生变化的时刻,而图中输出的data则为数据总线上的数据,并非alu_out的数据,有一点出入。当然,这也仅仅是个人理解。