ISE MAP 时报错(ML505开发板, bankless pin)

时间:10-02

整理:3721RD

点击:

在使用ML505开发板上的SPI Flash时,出现以下报错:ISE LOC constraint N15 on spi_sclk is invalid: No such site on the device.

网络查找,主要原因就是把spi_sclk这个信号分配到了一个不存在的引脚N15之上。

但是我在ML505的数据手册上是能够查到N15这个引脚的啊,不知道怎么回事?(同样的情况发生在P15引脚上)

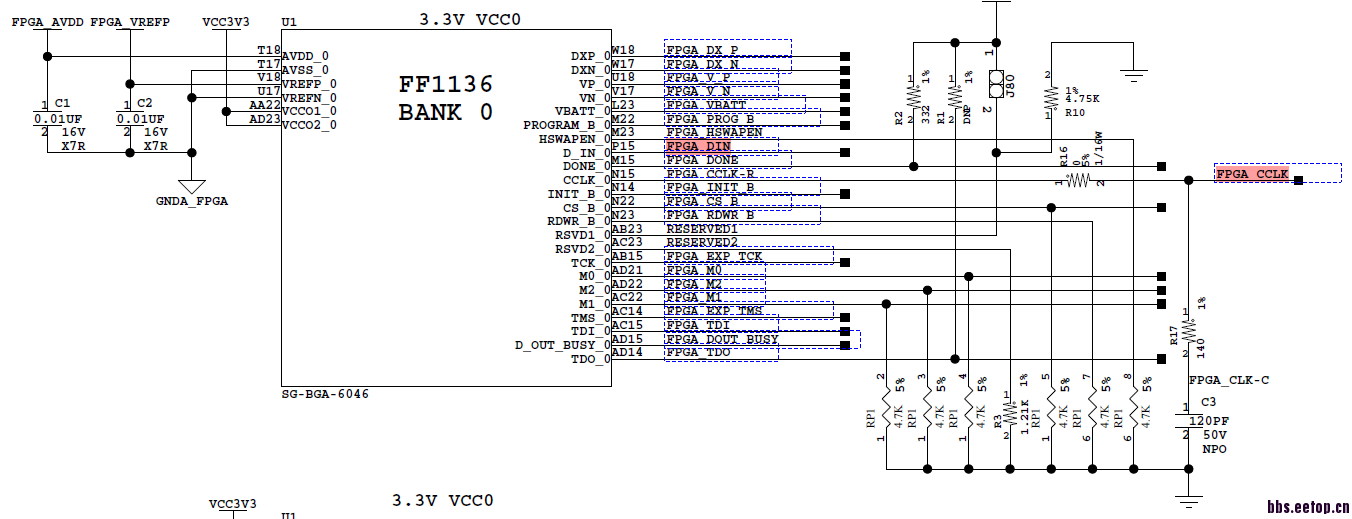

ML505的原理图如下图所示(FPGA_CCLK连接SPI_FLASH的时钟引脚,N15与其相连,中间还有个电阻)

用PlandAhead查看,发现N15和P15的属性是bankless pin, bank type是none。虽然它们在原理图上都属于Bank0。

针对这种情况,我该如何给其分配引脚呢?