DDR2 时序约束不满足

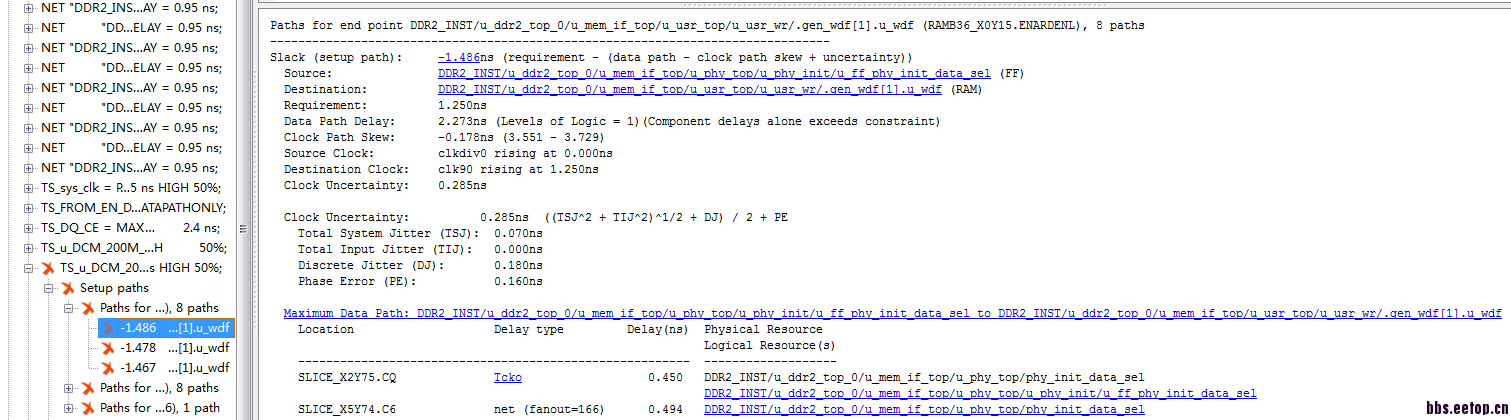

在ML505上使用的DDR的型号为MT4HTF3264-667,利用ISE 生成了MIG,频率设置为200M(5000ps)。在ISE建立了一个工程,顶层文件产生很简单的读写,直接调用MIG控制DDR,最后根据生成的ucf文件约束。发现时序约束不满足。如下图:

由于图太小,将不满足的路径描述如下:

由于图太小,将不满足的路径描述如下:Slack (setup path): -1.486ns (requirement - (data path - clock path skew + uncertainty))

Source: DDR2_INST/u_ddr2_top_0/u_mem_if_top/u_phy_top/u_phy_init/u_ff_phy_init_data_sel (FF)

Destination: DDR2_INST/u_ddr2_top_0/u_mem_if_top/u_usr_top/u_usr_wr/.gen_wdf[1].u_wdf (RAM)

Requirement: 1.250ns

Data Path Delay: 2.273ns (Levels of Logic = 1)(Component delays alone exceeds constraint)

Clock Path Skew: -0.178ns (3.551 - 3.729)

Source Clock: clkdiv0 rising at 0.000ns

Destination Clock: clk90 rising at 1.250ns

Clock Uncertainty: 0.285ns

我直接用MIG 生成的约束文件进行约束都不满足,不知道怎么改了。

自己分析下原因啊,Requirement: 1.250ns ,你不觉得有问题吗,虽然我不知道你的工程。

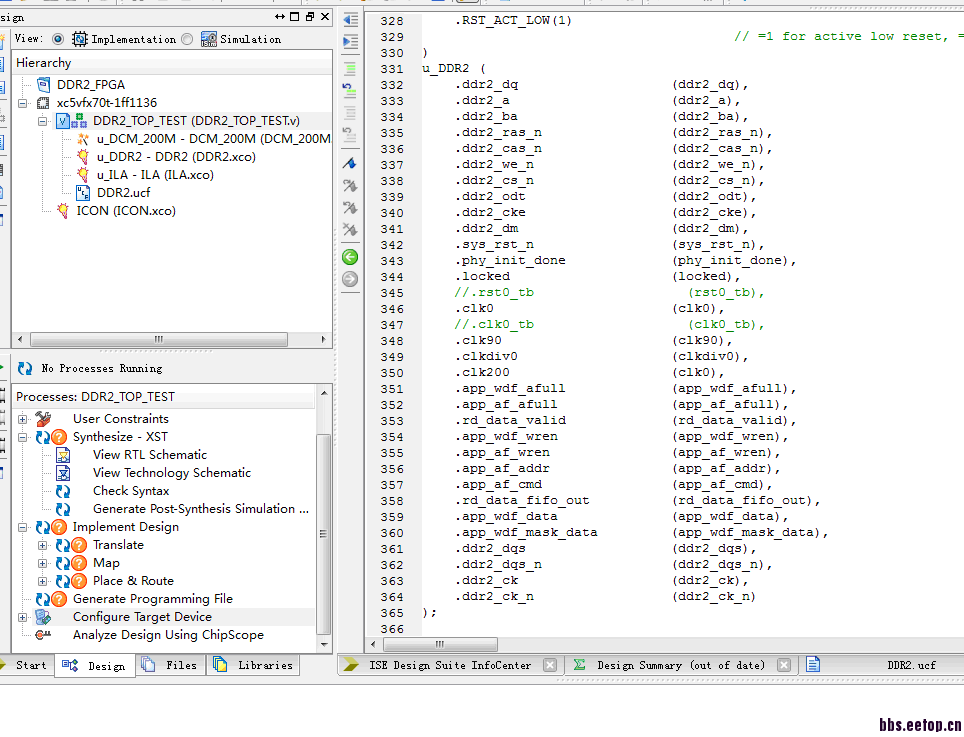

1.25ns计算的是clk90和clkdiv0他俩路径之间的约束,下面是我的工程:

下面是对时钟的约束:

你可以看下我下面编辑的工程和ucf的截图

要求时间1.25ns,但是你时钟只有200M,DDR最多也就400M,也就是2.5ns就行了,出来了1.25ns,说明你这里面的数据路径还有半周期的,也就是可能有上下沿混用的。你自己看看这条路径分析下,看能不能避免,或者没关系的。

我的时钟的确是有个90度的,和clkdiv0之间相差的就是1.25ns,这条路径是不该约束的。我在约束文件里写了

NET "clkdiv0" TNM_NET = FFS "clkdiv0_GRP";

NET "clk90" TNM_NET = FFS "clk90_GRP";

TIMESPEC TS_clkdiv0_TIG = FROM "clkdiv0_GRP" TO "clk90_GRP" TIG;

这样的时序约束,但是还是报错

没用过xlinx,不知道这种约束,也没用过它的DDR,所以也不知道他的工程,无法帮你。

1.如果这两个时钟域之间你本来就想异步处理,你可以将这两个clock设定成false path,ucf文件里面应该是设定成不同的group。

2.如果你的设计需要分析这两个时钟域之间的data,你需要设定multi path,就不应该分析1.25ns这两个rising edge,可以分析3.75,或者6.25对应的一对rising edge。multi path语法可以查阅xilinx 的 clock closure user guild。