modelsim模拟时出现# Error loading design问题

时间:10-02

整理:3721RD

点击:

module mealy_fsm1(clk, Bin, Bout);

input clk, Bin;

output Bout;

reg q0, q1, q2;

always @(posedge clk)begin

q0<=q1_bar;

q1<=q0;

q2<=~((~(q1_bar&q0_bar&Bin))&(~(q2_bar&q0&(~Bin)))&(~(q2&q1&q0)));

end

wire q0_bar = ~q0;

wire q1_bar = ~q1;

wire q2_bar = ~q2;

assign Bout = ~((~(q2_bar&(~Bin)))&(~(q2&Bin)));

endmodule

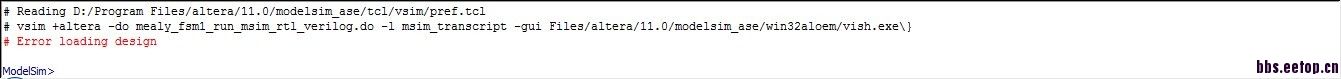

模拟时就出现下列问题了

# Reading D:/Program Files/altera/11.0/modelsim_ase/tcl/vsim/pref.tcl

# vsim +altera -do mealy_fsm1_run_msim_rtl_verilog.do -l msim_transcript -gui Files/altera/11.0/modelsim_ase/win32aloem/vish.exe\}

# Error loading design

我用quartus2编译后进行用modelsim进行模拟就出现了这个问题,折腾了一天实在是没办法了,请各位大神帮帮忙,我自己感觉是软件设置的问题,试验了其他的代码也是不行。

你的测试文件呢?

把文件完整贴一下。

还有,直接用modelsim建立工程仿真试一下

还是你编的程序有问题,虽然编译器认为没问题了,但是你仔细检查还是会发现问题的,我也遇到了类似的问题,但是仔细检查之后确实发现了一些问题,改完之后就好了