DDR2带宽利用率可以怎么测量

时间:10-02

整理:3721RD

点击:

小弟在使用V6 LX760做一个项目。ps:我们做的项目是关于视频拼接的。需要将capture的视频数据存储到memory中,再从memory中将capture存储的数据读取输出显示。

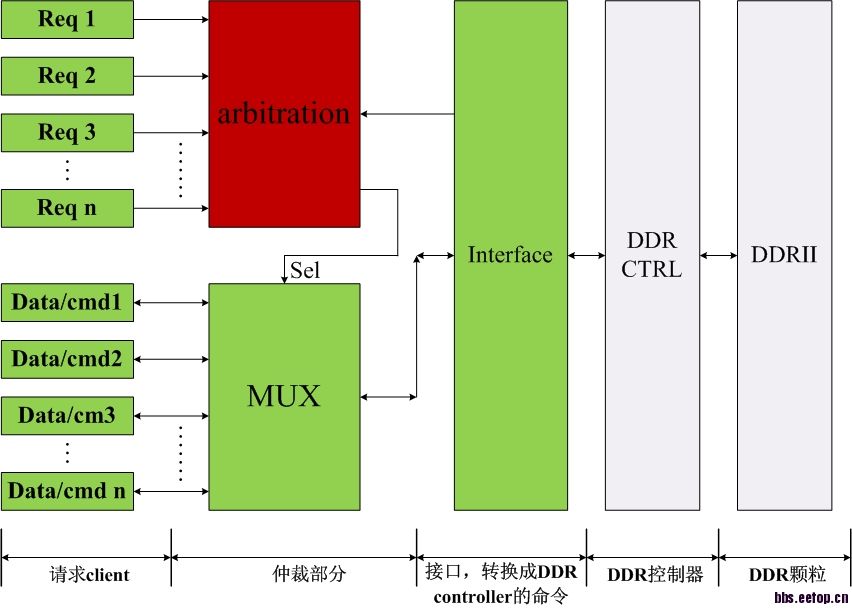

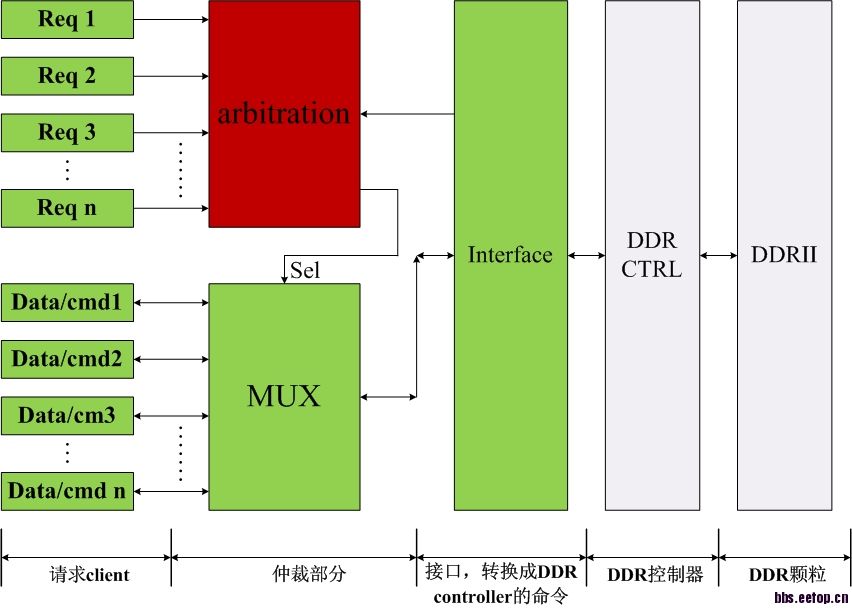

我主要是做和存储器相关的部分。主要包括:仲裁+DDRII控制器+DDRII颗粒。其中DDRII控制器是直接用xilinx的MIG核。

我想问下按照我附件中的实验架构可以怎样测量DDR效率?如果不可以,可不可以推荐一种比较好的测量DDR效率的方法?

如果按照实验架构测试DDR2效率,需要每个client都需要有访问,而且尽量将仲裁对DDR访问效率的影响也能cover到?

麻烦大牛指点下!

我主要是做和存储器相关的部分。主要包括:仲裁+DDRII控制器+DDRII颗粒。其中DDRII控制器是直接用xilinx的MIG核。

我想问下按照我附件中的实验架构可以怎样测量DDR效率?如果不可以,可不可以推荐一种比较好的测量DDR效率的方法?

如果按照实验架构测试DDR2效率,需要每个client都需要有访问,而且尽量将仲裁对DDR访问效率的影响也能cover到?

麻烦大牛指点下!

按照你的访问模型,发一些随机指令,仿真一下。

是的 ,读写混合在一起,地址可以是burst对齐的

你好,我已经仿真过了。现在就想测效率什么的,请问下可以怎么测量?

通过仿真一个读写命令,看看写你的数据需要耗费多少个时钟周期,再把刷新周期加入。就可以估算出读写效率。

发一组数据,看看时间,除一下就可以了。

连续的发送请求,看连续几个命令请求的时间点到DDR总线上执行的时间就是最快的效率

可以仿真测试

可以用每秒进出的数据量,即(写入的数据+读取的数据)/ddr2的理论带宽,就可以得到啦

同问~

看DDR2接口端DQS出时钟的比率就是带宽效率

求解,我也想知道