有关高清视频采集卡的方案

=============================

wzh 20121230

当前的视频采集卡有些采集的像素数和帧率已经达到惊人的地步。

例如有microvision MV-VGA420E 双路VGA采集卡

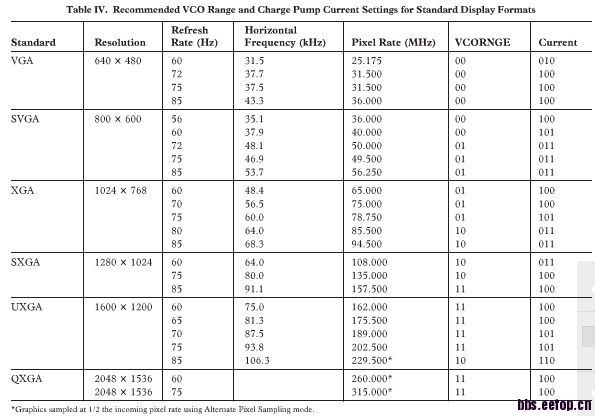

1、VGA模式:1920*1200/30帧;1920×1080/30帧;1600×1200/30帧;

1440×1050/30帧;1280×1024/30帧;1024×768/30帧;800×600/60帧,

最高采集分辨率可达2048*1536;

2、HD模式:可采集1080P 、720P、586P、480P逐行数字信号.

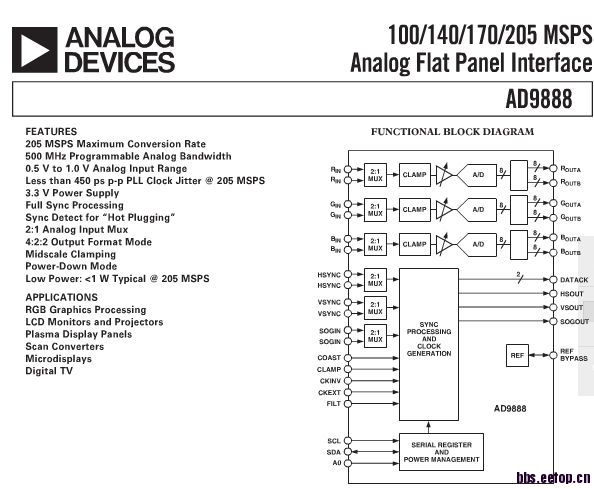

对照图片分析,可知采用的视频adc芯片可能为ad9888

对于这种采样输出clk达到205M的adc芯片,我估计采集视频卡使用的fpga最多是cyclone3的,同时存储ram

似乎是sdram【可能是ddr,但不像ddrII,因为II的颗粒一般是bga封装】

所以我就有下面疑问:

(1)cyclone3的输入对于205M支持吗?

(2)cyclone3支持的sdram一般不超过167M,常用的是133M,如何实现上面205M高速采样数据存储?

1、采样芯片AD9888输出的时钟不是固定的205M,而是采样的分辨率是多少像素时钟就多少,最大1600*1200@60HZ的162M像素时钟。

2、如果是SDRAM,那么AD9888输出的像素大小应该为16bit(4:2:2格式),而且需要两块SDRAM采1路视频。

如果是DDR,那么AD9888输出的像素大小则可以为16bit,1块DDR采1路视频;24bit-30bit的话需要2块DDR采1路视频。

谢谢 蓝色风暴@FPGA 。

如果是SDRAM,那么AD9888输出的像素大小应该为16bit(4:2:2格式),而且需要两块SDRAM采1路视频

这个似乎不是问题,你说的应该是8bit位宽的sdram,实际上使用16bit位宽,使用两片就可以采集24bit像素的数据了。

我所关心的是205m像素频率数据如何采集和存储。即使使用了ddr sdram,考虑2片16bit位宽的,那么ddr的时钟需要达到205M/2才能基本保证采集的像素不丢点写入sdram。这个使用cyclone3 7速度系列实现有风险吗?还有就是sdr的sdram可能实现吗?毕竟便宜啊。

==========================================

还有一点考虑,考虑到图像采集卡在如此高的分辨率下,采集帧率可能只有60Hz的1/4左右或者更少。那么

能否第一帧图像采集行1,行5,行9,……;第二帧图像采集2,6,10……,第三帧图像3,7,11,……第4帧图像4,8,12……。如此,采集使用1行时间,写入ram使用3行时间,这样的话,是否使用sdr sdram也能实现超大分辨率图像存储了?

我想可以只有接口是高速的205M,之后就串并转换,205/2=102.5M甚至更低来处理。

不知道你到底在考虑什么首先分辨率最大1600*1200@60HZ,时钟162M。分辨率再大,时钟也不会超过162M,即使4k*2k,时钟也只是148.5M。

所以你不要考虑205M的情况了。

205M别说在C2,就算在C5上逻辑电路也要写的特别小心,否则时序很难过,当然可以做到。

还有如果DDR跑300M,那么其实FPGA送给DDR的时钟是150M,双沿存数据。

另外你那样存法岂不是丢了很多数据,肯定不行的,我们是存一帧数据,而不是存多帧数据。

这块板采集速率不怎么样啊,我们的产品都挂8片DDR3了、

c3逻辑跑205是可以的,RAM似乎不行。

所以有次用FF阵列来存RAM。

分辨率再大,时钟也不会超过162M,即使4k*2k,时钟也只是148.5M。

这个不太理解,有请蓝色风暴@FPGA仔细讲下,谢谢了

为什么需要205M?可以两个点并行处理啊!那就102.5M,存储器不能光看速度,还要看位宽,比如人家是32位宽的!

asyou说的有道理。

ad9888就是提供24bit和48bit位宽两种,速度可不就是降了一倍啊

不用猜是什么芯片,讨论有可能是建立在不正确的假设上的。

确定芯片的型号。再讨论。

比如把芯片取下,去掉散热片,仔细看看型号。

另外输入不同的信号,用示波器量一下板子上的信号

最简单的处理方案是什么