恳请用过AHB总线的大侠指点迷津

然后,device1 和 device2 (相同功能)开始并行地对自己RAM中的数据进行处理,结果存回自己RAM的特定位置;

当2个设备都处理完毕后,允许device1 访问 device2 的RAM 并且把device2的结果读入device1的RAM中,与device1的结果合并;

然后 device1 开始处理 “合并后的结果”(作为这一轮的device1的输入数据);

最后,当 device1处理完毕后,device3 开始顺序地访问RAM1 和RAM2;

大概就是这样的dataflow。我说的很罗嗦,但是应该不算复杂。

请问这样的系统用AHB总线合适吗?应该怎么想。

一般大侠们,都是如何通过总线互联设备的?从头自己写一个总线吗?还是稍微改一些标准的设计。

刚才只是想解释一下数据流图,即,谁需要和谁通信。

如果我硬往AHB总线上套用,就搞不明白到底谁是主设备,谁是从设备。(感觉一个模块它有时是主设备,有时又充当从设备)

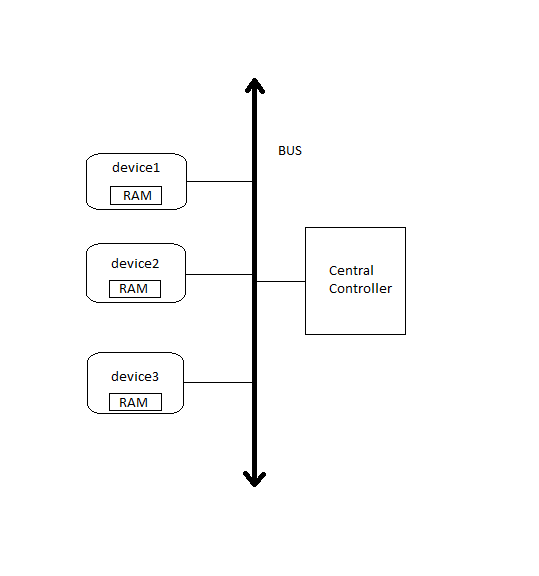

如果我让Controller充当主设备,所有的device充当从设备,套用AHB的图就是如下结构:

因为我想让slave之间数据传输,就必须让Controller先读 device_i 中的数据,然后由controller再将数据写入 device_j. 这就是小弟目前能想到的,感觉效率不高啊(我太弱了。

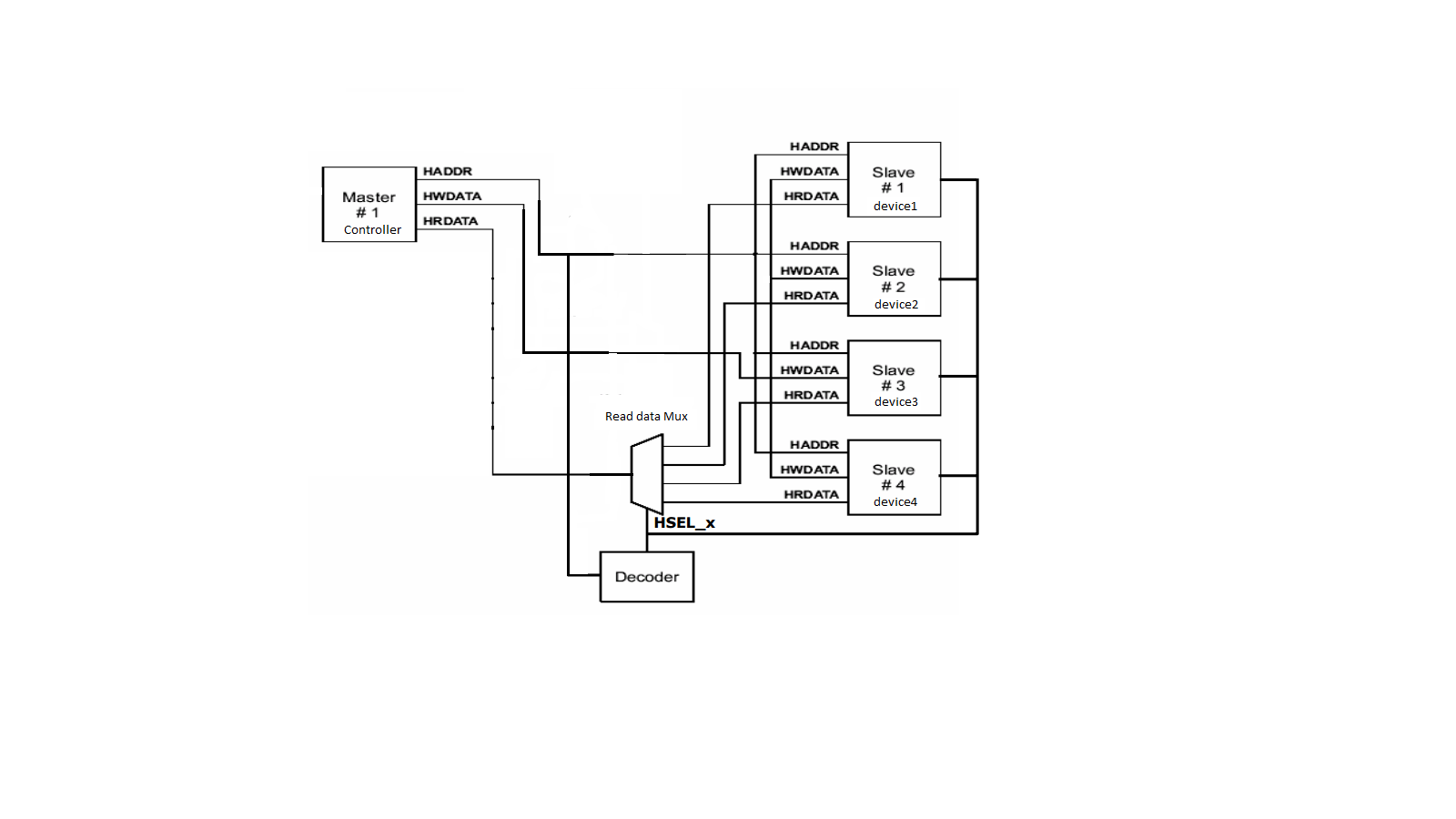

可以考虑把RAM也挂到AHB,设计一个slave接口,device作为master通过总线访问RAM。

学习学习

如果一个device又是主设备又是从设备,那么就定义一个master1和slave1挂在这个device的interface上就ok。

AHB可以搞定的。

按rvnistelrooy说的,把RAM也作为slave;或者给RAM分配一段地址,允许通过device1或者device2的AHB interface访问RAM。

同意楼上的看法

谢谢各位大侠回帖。

因为一个时刻只能1个master享用总线,不可能只用AHB总线来实现master1,2,3并行访问slave1,2,3.

(1)所以我可不可以 在 “通信阶段” 使用AHB(device是master, ram是slave), 在“并行处理阶段” 直接抛开AHB,device1连接RAM1, device2连接RAM2。

(2)我想用最快方式把RAM1中的某些数据读入RAM2中,每个字都是先RAM1 Read,然后RAM2 Write吗?这个时序我高不太清楚。

(3)AHB是能拿来直接用(稍作改动)的code吗?还是只是一个协议,都是从头自己写的?

谢谢你的指点,很有帮助:)

请问AHB是一个现成的设计(有现成的verilog code可以下载,根据需要改改参数就行),还是只是一个协议(一切都要自己从头搭建)?

还有一个关于burst mode的问题:

这和SRAM的产品有关吧?我新手,从书本上看SRAM也就是Address, Data, CS, WE, OE这5个pin吧(我们学生用的行为级模型),那么大侠们一般是怎么实现Burst模式的啊?

我现在做的 研究生毕设,和你做的很像,求交流