TimeQuest做时序分析时遇到hold违约,求教如何解决?

时间:10-02

整理:3721RD

点击:

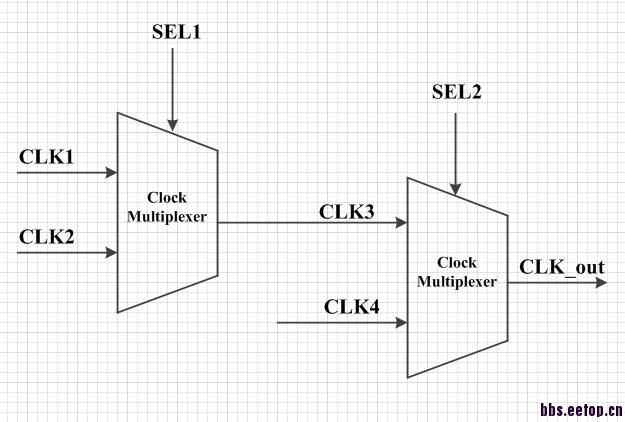

rt,小弟最近在用altera做一个fpga的工程。需要用到两个串联的时钟复用器,如下图所示:

clk_out最后是给了altera自带双口ram的写时钟断。在做apr后的时序分析时,有警告:

clk_out最后是给了altera自带双口ram的写时钟断。在做apr后的时序分析时,有警告:Critical Warning: Timing requirements not met 仔细看了报告里的描述,应该是hold的时序违约。我用的是TimeQuest做的,sdc如下:

###########################################################################

#

# Generated by : Version 9.1 Build 222 10/21/2009 SJ Full Version

#

# Project : spi_80

# Revision : spi_80

#

# Date : Thu Nov 20 10:16:34 CST 2014

#

###########################################################################

# WARNING: Expected ENABLE_CLOCK_LATENCY to be set to 'ON', but it is set to 'OFF'

# In SDC, create_generated_clock auto-generates clock latency

#

# ------------------------------------------

#

# Create generated clocks based on PLLs

derive_pll_clocks -use_tan_name

#

# ------------------------------------------

# Original Clock Setting Name: WRB

create_clock -period 200 -name {WRB_SCL_i} {WRB_SCL_i}

# ---------------------------------------------

# Original Clock Setting Name: SCK

create_clock -period 200 -name {SCK_i} {SCK_i}

# ---------------------------------------------

# Original Clock Setting Name: rCLK_ram

create_clock -period 200 -name rCLK_ram [get_ports {gram_rck}]

# ---------------------------------------------

create_clock -period 100 -name dotclk [get_ports {dotclk}]

# ** Clock Latency

# -------------

# ** Clock Uncertainty

# -----------------

# ** Multicycles

# -----------

# ** Cuts

# ----

# ** Input/Output Delays

# -------------------

# ** Tpd requirements

# ----------------

# ** Setup/Hold Relationships

# ------------------------

# ** Tsu/Th requirements

# -------------------

# ** Tco/MinTco requirements

# -----------------------

#

# Entity Specific Timing Assignments found in

# the Timing Analyzer Settings report panel

#

# ---------------------------------------------

# The following clock group is added to try to

# match the behavior of:

# CUT_OFF_PATHS_BETWEEN_CLOCK_DOMAINS = ON

# ---------------------------------------------

set_clock_groups -exclusive -group {SCK_i} -group {WRB_SCL_i} -group {rCLK_ram} -group {dotclk}

# ---------------------------------------------

请问大神们如何能解决这个hold违约啊?貌似跟时钟周期没有关系啊。新手求指导!非常感谢!

同样菜鸟一个 求大神解答

顶一下,还是没有解决。现在重新改下代码再试下

问题解决了:assignments-setting-filter-Settings-optimize hold timing 选择all path

感谢csdn的net_xurong:http://blog.csdn.net/net_xurong/article/details/4885756