Xilinx Spartan6 block ram调用问题

我现在想要fpga内部的block ram和flash通信,flash是spi接口的,一个基本的flash controller我已经写好了,现在就是ram的数据读取问题。

我非常困惑的是这样reg [15:0] bram[(128-1):0]; 定义一个ram的意思是让fpga自己分配地址吗?还是这只是在仿真软件中的一种应用,不能在硬件中成立?

另外我看到一些有关例化ram的帖子,类似:

module bramtest(

input clk,input rst_n,

input ram1_en,

input [7:0] dina,

input [2:0] addr,

input wea,

output [7:0] douta

);

ram1 sp_ram (

.clka(clk), // input clka

.rsta(rst_n), // input rsta

.ena(ram1_en), // input ena

.wea(wea), // input [0 : 0] wea

.addra(addr), // input [2 : 0] addra

.dina(dina), // input [7 : 0] dina

.douta(douta) // output [7 : 0] douta

);

endmodule

-------------------------引用自cqugjw

[求助] Xilinx开发板Block RAM的使用

这个是放在哪里呢?芯片的说明文件,Spartan-6 Libraries Guide for HDL Designs.pdf中也有例化ram的verilog,这段代码是放在哪里?单独建立一个模块?

最后一个问题是,我希望ram能够读写flash,同时也希望别的host能读写ram,应该如何应用?

希望大家多多帮助水深火热中的程序媛,谢谢了。

可以直接在硬件中使用啊,类似寄存器数组一样,一般会例化成Block RAM,有的综合时打散使用寄存器reg1, reg2, reg3,

代码放在你想调用的模块那里,作为底层例化,至于.v文件,加入到project中即可,和普通的module一样处理。你问的是这个吗?

最后的问题,RAM能读写FLASH,别的HOST能读写RAM,你这说的啥意思?RAM只是存储对象,你有控制逻辑去读写RAM,自身无法主动访问别的对象啊。

应该是有段代码,读一段数据,然后把数据通过SPI写到FLASH,或者反过来从FLASH中读取数据,写到RAM中,简单的实现即可,要高效就要使用DMA之类的了。

别的HOST当然可以访问RAM,只要有读写通道过来就行。

不会,友情帮顶

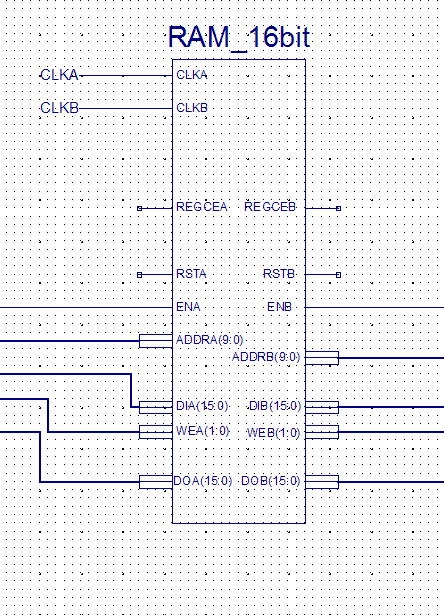

非常感谢,我今天有点理清头绪了,TDP ram也成功例化了,下面就是写一个你说的让ram 和spi flash通信的东西了。

我以前用的是HDL designer,是可以模块化设计的,不知道ISE是不是也可以这样呢?我这个例化的ram只要当成其中一个模块就可以了是吗?

对啊,ISE只是工具,HDL通用的东西ISE自然也支持,只是ISE是专门用于FPGA的,所以会支持些具体的器件和原语,比如coregen生成的IP,比如时钟生成模块,block memory等,

我现在直接用XPS 中的IP核的

schematic里面,我想要把输入信号赋值为零如何操作呢? 比如我想把RSTA赋值为零的话有办法吗?

再补充一个问题 true dual port ram的clka 和clkb不能用同一个信号吗?我试图都用系统时钟,结果提示这样相当于他俩短路。

电路图模式的我不会,通常直接代码搞定。当然两时钟可以用同一source,这个没关系,我们用得更多的模式就是一个口写,另外个口读;你要是配置成两口都可读写也没问题。

真的很谢谢你,我又碰到一个新问题,我程序在modelsim里面仿真没有问题,但是放到ISE上就报错,程序如下,我实在看不出问题,不好意思了Assignment under multiple single edges is not supported for synthesis

INFO - You can change the severity of this error message to warning using switch -change_error_to_warning "HDLCompiler:1128"

always@(posedge sclk or posedge reset)

begin

if((delay_count_page>=4)&&(delay_count_page<=259)&&(~delay_count_page%2)&&read_en)

begin

case(delay_count_byte)

4'd1:data[7]<=miso;

4'd2:data[6]<=miso;

4'd3:data[5]<=miso;

4'd4:data[4]<=miso;

4'd5:data[3]<=miso;

4'd6:data[2]<=miso;

4'd7:data[1]<=miso;

4'd8:data[0]<=miso;

default: data<=0;

endcase

end

else if((delay_count_page>=4)&&(delay_count_page<=259)&&(delay_count_page%2)&&read_en)

begin

case(delay_count_byte)

4'd1:data[15]<=miso;

4'd2:data[14]<=miso;

4'd3:data[13]<=miso;

4'd4:data[12]<=miso;

4'd5:data[11]<=miso;

4'd6:data[10]<=miso;

4'd7:data[9]<=miso;

4'd8:data[8]<=miso;

default: data<=0;

endcase

end

else if((delay_count_page>=3)&&program_enable)

begin

if(delay_count_page>=3&&delay_count_page<=258&&(delay_count_page%2))

begin

if (delay_count_byte==8)

data<=dob;

end

end

else

data<=16'd0;

end

非常感谢你。不好意思啊,我又遇到一个新问题,程序在modelsim上仿真没有问题,但是转到ISE上就报错,错误和代码如下,我实在不太明白是什么问题,麻烦你给看看。

ERROR:HDLCompiler:1128 - "D:\EDK_project\MDIO_Communication\flash_controller.v" Line 329: Assignment under multiple single edges is not supported for synthesis

INFO - You can change the severity of this error message to warning using switch -change_error_to_warning "HDLCompiler:1128"

Module flash_controller remains a blackbox, due to errors in its contents

always@(posedge sclk or posedge reset)

begin

if((delay_count_page>=4)&&(delay_count_page<=259)&&(~delay_count_page%2)&&read_en)

begin

case(delay_count_byte)

4'd1:data[7]<=miso;

4'd2:data[6]<=miso;

4'd3:data[5]<=miso;

4'd4:data[4]<=miso;

4'd5:data[3]<=miso;

4'd6:data[2]<=miso;

4'd7:data[1]<=miso;

4'd8:data[0]<=miso;

default: data<=0;

endcase

end

else if((delay_count_page>=4)&&(delay_count_page<=259)&&(delay_count_page%2)&&read_en)

begin

case(delay_count_byte)

4'd1:data[15]<=miso;

4'd2:data[14]<=miso;

4'd3:data[13]<=miso;

4'd4:data[12]<=miso;

4'd5:data[11]<=miso;

4'd6:data[10]<=miso;

4'd7:data[9]<=miso;

4'd8:data[8]<=miso;

default: data<=0;

endcase

end

else if((delay_count_page>=3)&&program_enable)

begin

if(delay_count_page>=3&&delay_count_page<=258&&(delay_count_page%2))

begin

if (delay_count_byte==8)

data<=dob;

end

end

else

data<=16'd0;

end

//---------------------------------------------------- //store miso to data& get data from dob

always@(posedge sclk)

begin

if(read_en)

begin

if((delay_count_page>=4)&&(delay_count_page<=259))

begin

if(~delay_count_page%2)

begin

case(delay_count_byte)

4'd1:data[7]<=miso;

4'd2:data[6]<=miso;

4'd3:data[5]<=miso;

4'd4:data[4]<=miso;

4'd5:data[3]<=miso;

4'd6:data[2]<=miso;

4'd7:data[1]<=miso;

4'd8:data[0]<=miso;

default: data<=0;

endcase

end

else if (delay_count_page%2)

begin

case(delay_count_byte)

4'd1:data[15]<=miso;

4'd2:data[14]<=miso;

4'd3:data[13]<=miso;

4'd4:data[12]<=miso;

4'd5:data[11]<=miso;

4'd6:data[10]<=miso;

4'd7:data[9]<=miso;

4'd8:data[8]<=miso;

default: data<=0;

endcase

end

end

end

else if(program_enable)

begin

if(delay_count_page>=3&&delay_count_page<=258&&(delay_count_page%2))

begin

if (delay_count_byte==8)

data<=dob;

end

end

else

data<=0;

end

我改了一下 好像可以了。

WARNING:Xst:2042 - Unit top: 44 internal tristates are replaced by logic (pull-up yes):

这个warning是什么意思呢?

注意查看错误提示,一般会告诉你在哪里支找原因。Assignment under multiple single edges is not supported

再看你代码,哪里与edge有关的? (posedge sclk or posedge reset)

我们通常用是这么用,

always @ (posedge clk or posedge reset)

if (reset == 1'b1)

....

else

就是reset作为复位信号,你的代码没有下面的reset部分,代码就会认为这是个clock采样,变为多时钟采同一个数据,所以报错了。

这错误提示说得很清楚啊,还不清楚自己google

是用条件划分状态机比较好 还是一个状态机内部划分条件比较好

通俗来说就是两个个if 是分为状态机好,还是在一个状态机内依次if好

顶顶顶顶顶

一般这种情况是你的代码里面有不可综合的语句

一般这种情况是你的代码里面有不可综合的语句