在做按键消抖verilog程序时,出现问题,求助

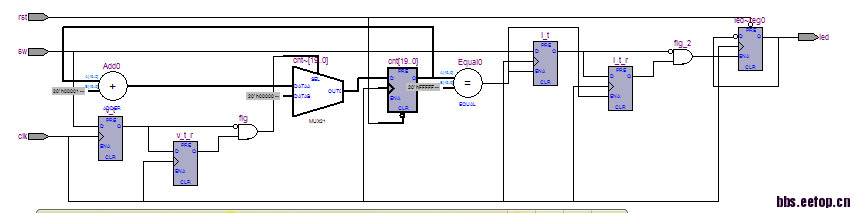

上图是按键的消抖电路

下图是仿真波形

代码

module key(

rst,clk,sw,led

);//¶¨ÒåÁË4¸ö¹Ü½Å

input rst,clk,sw;

output led;

reg led;

//±ßÑؼì²â·¨£¬swÊÇ·ñ¾ßÓеçƽµÄÕý·´×ª

reg v_t;//Õâ¸öÊÇÀ´´æ´¢sw´Î״̬µçƽµÄ¼Ä´æÆ÷

reg v_t_r;//Õâ¸öÊÇÀ´´æ´¢Ê×״̬µçƽµÄ¼Ä´æÆ÷

wire flg;//Õâ¸öÊÇÀ´¼ì²â´æÔÚµçƽµÄÕýÏò·´×ªµÄ

always @(posedge clk)//ÔÚÕâ±ß¾ÍÊÇÀ´¼ì²âµçƽµÄ£¬ËùÒÔÊDz»ÐèÒªµÄ,,,ÔÚverilogÖУ¬Ò»¸ö¼Ä´æÆ÷¾ÍÊÇдһ¸öalways

v_t<=sw;

always @(posedge clk)

v_t_r<=v_t;

assign flg=v_t_r && (~v_t);//Õâ¸ö¾ÍÊÇÓÃÀ´¼ì²âµÄ±êÖ¾

//²¢ÐÐÔËÐеÄ

//ÏÖÔÚ¾ÍÀ´ÉèÖõçÆ¿Õðµ´µÄʱ¼ä

reg [19:0] cnt;//ÉèÖõÄʱ¼äÊÇ20ms£¬£¬£¬ËùÒÔÔÚÕâ±ßÊÇ20λµÄ

always @(posedge clk or negedge rst)

if (!rst)

cnt<=20'h0;

else if(flg)

cnt <=20'h0;

else

cnt<=cnt+1'b1;

//ËùÒÔÔÚÊý×Öµç·Öл¹ÊÇÏÈÒª½«Ê±ÐòÏÈ» ³öÀ´µÄ

//ÔÚÕâ±ßÍê³ÉµÄÊǶԺãÎÈÐźŵIJÉÑù

reg l_t;

reg l_t_r;

always @(posedge clk)

if(cnt ==20'hfffff)

l_t<=sw;

always @(posedge clk)

if(cnt ==20'hfffff)

l_t_r<=l_t;//ÔÚÕâ±ß»á²úÉúreg?

wire flg_2;

assign flg_2=l_t_r && (~l_t);

always @(posedge clk or negedge rst)

if(!rst)

// led_ctrl <=1'b0;

led<=1'b1;

else

if(flg_2)

// led_ctrl<=~led_ctrl;

//assign led=led_ctrl?1'b1:1'b0;

led<=~led;

/*

always @(posedge flg_2 or negedge rst)

if (!rst)

led<=1'b1;

else

led<=~led;

*/

endmodule

怎么解决啊!

代码重新贴过,,,

module key(

rst,clk,sw,led

);

input rst,clk,sw;

output led;

reg led;

reg v_t;

reg v_t_r;

wire flg;

always @(posedge clk)

v_t<=sw;

always @(posedge clk)

v_t_r<=v_t;

assign flg=v_t_r && (~v_t);

reg [19:0] cnt;

always @(posedge clk or negedge rst)

if (!rst)

cnt<=20'h0;

else if(flg)

cnt <=20'h0;

else

cnt<=cnt+1'b1;

reg l_t;

reg l_t_r;

always @(posedge clk)

if(cnt ==20'hfffff)

l_t<=sw;

always @(posedge clk)

if(cnt ==20'hfffff)

l_t_r<=l_t;

wire flg_2;

assign flg_2=l_t_r && (~l_t);

always @(posedge clk or negedge rst)

if(!rst)

led<=1'b1;

else

if(flg_2)

led<=~led;

endmodule

是最后的那个reg的问题,,,但就是不知道怎么解决啊

添加条件,使cnt计数到FFFFF后停止计数

你的波形和你的代码是一致的啊!

最主要,你程序的目的是什么?

最后一个REG没有把SW给到它吧,你是想打两拍,但是实际条件不满足啊

这个我后来是通过异步的始终解决的,直接添加了 always @(posedge flg_2),,,,,但是会出现warning,,,内容就是利用reg 来做时钟

没有看代码,看你上面的回复 应该是想采 flg_2的上升沿。

很简单啊,把 flg_2打一拍 得到flg_2_dly 判断 flg_2 == 1'b1 && flg_2_dly == 1'b0 就可以了。

添加条件,使cnt计数到FFFFF后停止计数,并归零,最后一个always改为

always @(posedge clk or negedge rst)

if(!rst)

led<=1'b1;

else

if(l_t_r)

led<=~led;

试试

好的,,今天试一下

就是按键消抖

楼上正解,,,我试一下你的方法

always @(posedge clk)

if(cnt ==20'hfffff)

l_t<=sw;

always @(posedge clk)

if(cnt ==20'hfffff)

l_t_r<=l_t;

第二个always中 把if(cnt ==20'hfffff)这句删掉应该就可以吧,应该是检测相邻两个时钟周期的变化。