图形化Verilog编程,大家怎么看?

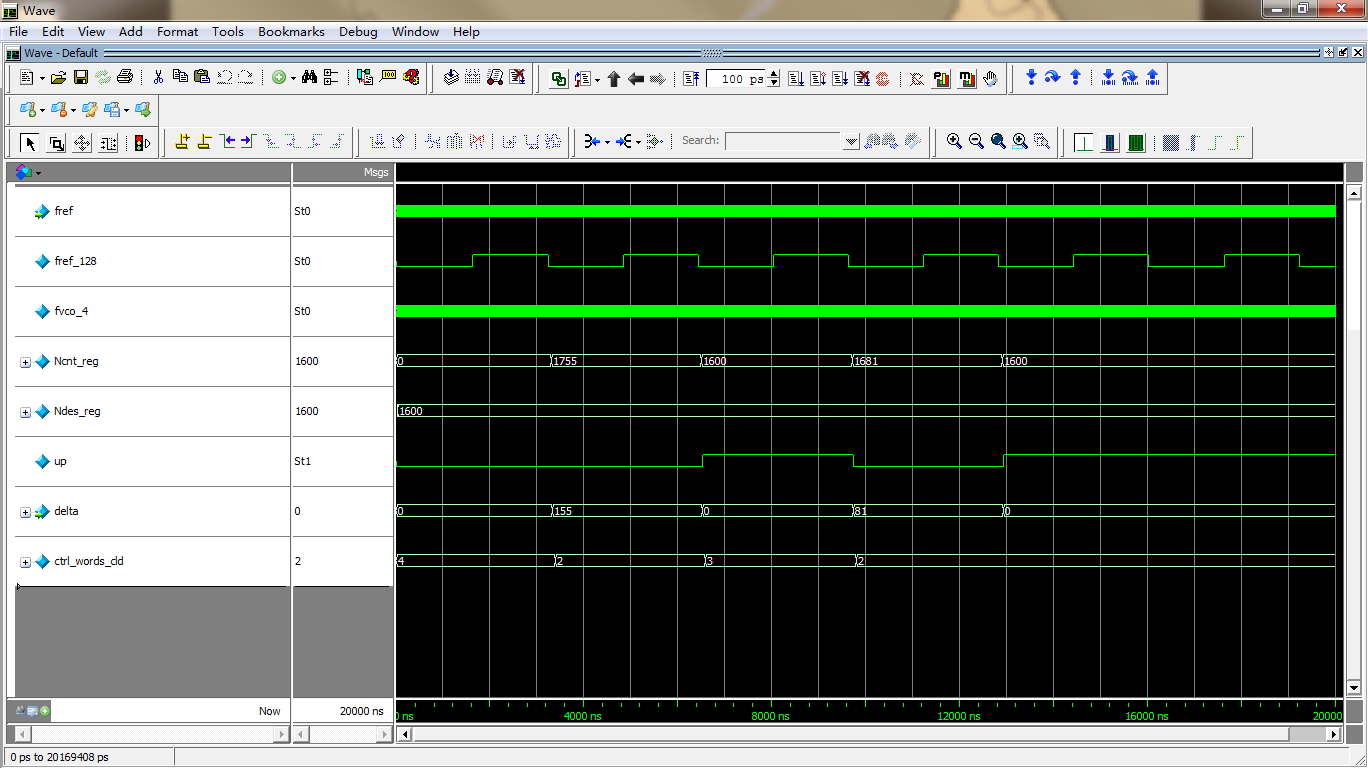

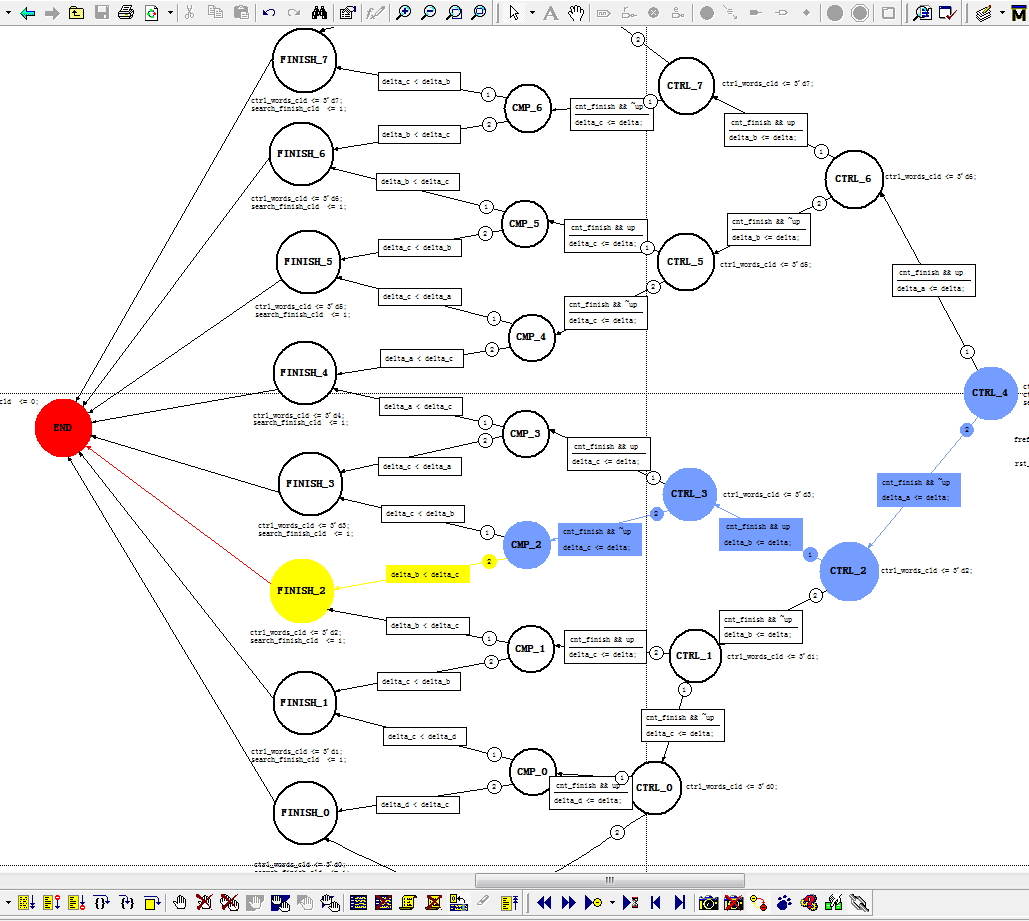

用Mentor Graphics 的 HDL Designer 来图形化设计状态机,算法状态机,非常方便,而且支持交互仿真,既可以查看波形,又可以对应到状态图中具体的状态。自动生成的代码 绝对可综合,且很规范。

另外,MATALB推出的HDL Coder基于simulink来设计数据通路,再自动生成代码,虽然用 matlab coder 设计算法状态机不方便,冗余(因为它不支持这样的操作符“<=”)。但是他设计数据通路还是非常快的。

而Mentor Graphics的HDL Designer图形化设计算法状态机,数据通路都是十分方便。

总之,基于图形化的自动代码综合技术,大大节省了开发时间,而Mentor Graphics的HDL Desiger更是十分方便。

这尼玛是RTL设计的一场革命吗?

表面上看解放了体力劳动,节约了设计时间。

但其实对设计者有更高的全局化,结构性把握的要求。

其实我觉得能把matlab系统的simlink直接转换为verilog就不错了,能节省工程师的很多时间。

现在都是系统设计工程师先在matlab里搭建结构,仿真通过后,前端设计人员再转为verilog,然后进行数据比对,来验证模型的正确性,形成电路实现。

感觉用处不大

能show和能用,差别很大

小编,对这些自动代码生成,都不看好吗? 但是感觉复杂状态机的设计,用图形化设计还是要方便很多。

而matlab 也一直在推他家的HDL coder,不过,代码生成的质量很低,尤其对于算法状态机方面。

但是HDL Designer 的代码生成还是相当不错

个人觉得只是习惯问题,现在很多工程师用惯了HDL,在写代码之前基本上心中对电路就有谱了,用HDL只是把它写出来而已,和画图的方式是一样的。

一般在写状态机之前也会手工画状态转移图吧,除非是状态机很简单,一看就明白。

不习惯

个人观点,跟习惯无关,现在的厂商想的都是怎么把c/c++阵营的人直接拉入FPGA开发中,降低FPGA开发的门槛,扩大FPGA阵营。

对于简单的设计,图形化、c、c++翻译当然没问题;

但是对于稍微复杂的设计,前路漫漫,如果抓不住这些复杂设计,

实际也降低不了FPGA开发的门槛。

看看现在厂家自己出的编译器的易用性、效率就知道了,如果再加一层c to hdl的翻译,

敢想象么

先把专业工具做的好一些,效率提高一些才是王道。

PCB软件发展了很多年了,也有anto route功能,但是有几个板子敢auto route出来呢?

前路漫漫,且看各厂家功力如何把。

类似原理图输入的设计方法,继承性不好

不可能火起来的,想想为什么都是各种语言代替传统的方式。

个人觉得,用HDL描述之前你就该有一个电路的实现方法了,所以图形化与否其实没有太多意义吧。所谓HDL,是描述,而非设计。心中有电路了,用图形用文字其实没有什么区别吧。

感觉这是设计大系统时用的,而且模块得由工程师来自己定制,小系统还用不着这样

感觉mentor graphics的图形输入方法从方法论上讲没有创新,不会比RTL实现法有更便利之处,相反MATLAB simulink从算法仿真到代码实现到是不错的方法。