占空比1:2的5分频

初始时钟占空比为1:1,要求5分频,分频后占空比1:2。

今天的笔试题,不会做。

请前辈指点。

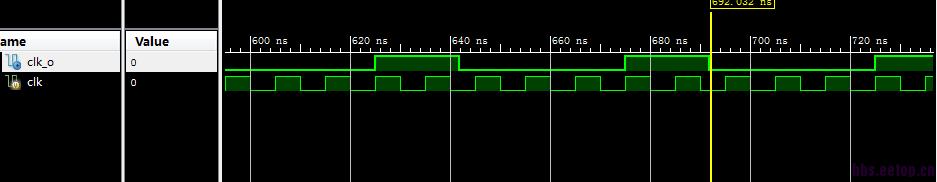

always @(posedge clk)

if(cnt>5)

cnt<=3'b0;

else

cnt<=cnt+1'b1;

always @(posedge clk)

h2<=(cnt==3'h2);

always @(posedge clk)

h34<=(cnt>2);

assign result=(h2^clk)||h34;

应该是可以的吧

占空比1:2,那么5个周期总共是(1+2)*5=15个时间单位,

分频后的时间为5:10,

5 = 2 + 1 + 2

10 = (1+2) + (1+2) + (1+2) + 1

分频前:

__ __ __ __

|____| |____| |____| |____| |____|

分频后:

___________________

|___________| |

占空比1:2,那么5个周期总共是(1+2)*5=15个时间单位,

分频后的时间为5:10,

5 = 2 + 1 + 2

10 = (1+2) + (1+2) + (1+2) + 1

分频前:

__ __ __ __

|____| |____| |____| |____| |____|

分频后:

_______________________

|____________| |

呵呵,看了楼上的回答,感觉题有歧义:

第一种理解:给的频率占空比为1:1的,得出1:2占空比的5分频;(我开始的理解)

第二种理解:给的频率占空比为1:2的,得出它的5分频;(楼上的方法)

小编要的是哪一种啊?

对不起,我没表述清楚。

要的是第一种。

对不起,我的题目没有表述清楚。

初始时钟占空比是1:1,要求5分频,分频后占空比为1:2

不可能每5个时钟就能分出小编希望的波形

但可以在15个时钟内分出3个时钟,总的占空比统计为1:2。(这可能也是出题者的本意)

如

原始时钟:1010101010 1010101010 1010101010

分频时钟:1111000000 1110000000 1110000000

占空比:

在一串理想的脉冲周期序列中(如方波),正脉冲的持续时间与脉冲总周期的比值?

恩 同意8楼

先将原时钟3倍频,再做分频,就可以做出1:2的占空比的5分频了

谢谢你的解答

无奈之下,我也是这么回答的

不过感觉应该不是正确答案

8楼正解!

10被3除不了啊...

8楼讲得不错

要写代码还是画电路图?

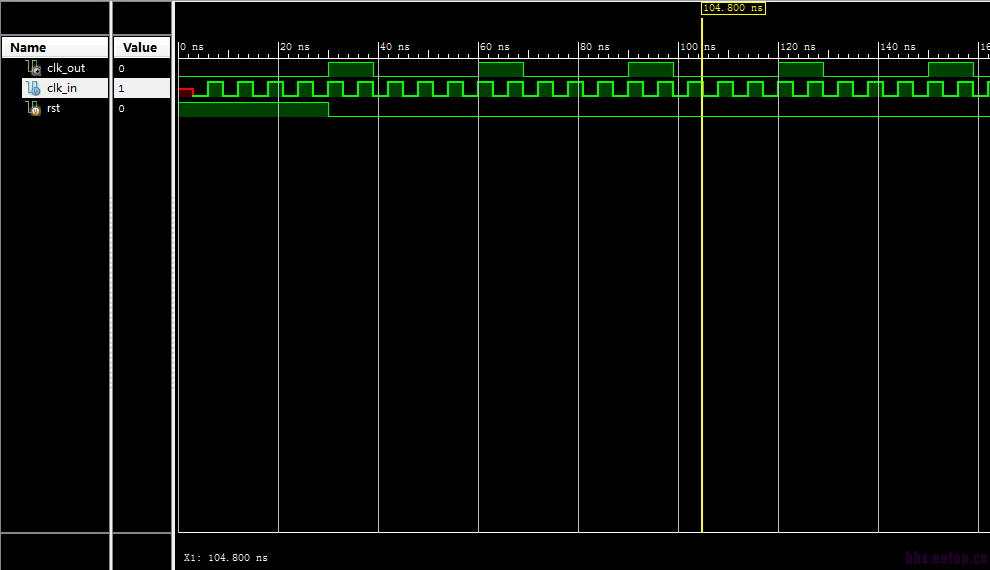

- module top(clk_in ,rst,clk_out

- );

- input clk_in;

- input rst;

- output clk_out;

- wire clk_out;

- reg clk_po;

- reg clk_ne;

- reg [3:0]cnt_po;

- reg [3:0]cnt_ne;

- always @(posedge clk_in or posedge rst)

- begin

- if(rst)

- begin

- cnt_po<=4'b0000;

- clk_po<=1'b0;

- end

- else

- begin

- if(cnt_po==4'b0100)

- begin

- cnt_po<=4'b0000;

-

- end

- else

- begin

- cnt_po<=cnt_po+4'b0001;

- if(cnt_po==4'b0000)

- clk_po<=1'b1;

- if(cnt_po==4'b00001)

- clk_po<=1'b0;

- end

- end

- end

- always @(negedge clk_in or posedge rst)

- begin

- if(rst)

- begin

- cnt_ne<=4'b0000;

- clk_ne<=1'b0;

- end

- else

- begin

- if(cnt_ne==4'b0100)

- begin

- cnt_ne<=4'b0000;

- end

- else

- begin

- cnt_ne<=cnt_ne+4'b0001;

- if(cnt_ne==4'b0000)

- clk_ne<=1'b1;

- if(cnt_ne==4'b0001)

- clk_ne<=1'b0;

- end

- end

- end

- assign clk_out=clk_po|clk_ne;

- endmodule

这样不行吧,实现的是30%的占空比

这种用一个锯齿波然后设定一个阈值比较一下即可,就是常见的PWM生成器

这个锯齿波怎么生成?用各种模拟器件吗?

同意楼上

感谢小编分享

弄来要多学习啊

这些都是点基础的

对时钟五分频,如果占空比是2:3这样的好弄,但要做到1:2,就要使高电平持续时间是三分之五个周期,这对原时钟计数的方法就不能实现;我想可否这样:用PLL对原始种产生一个120度相移的同频子时钟,分别用两个计数器对他们计数,然后对比两个计数器的值控制所产生时钟的高低电平时间,我想可以达到目的。我没有亲自试,还请大家指正!

哦,应该是240度相移。

通过累加器分频法即可,选择合适的模值和步长就可以无限逼近所要求的分频比及占空比。但是这只是一种近似,而且相互和分频周期大小是不恒定的。实际应用中采用芯片自带的IP核分频。