管脚分配出现的问题

时间:10-02

整理:3721RD

点击:

Error (171172): Detected conflicting assignments for the following nodes.

Error (171173): Node flag from partition Top cannot preserve previous placement at PIN B10 and honor the location assignment to PIN C14 这个如何解决啊

Error (171173): Node flag from partition Top cannot preserve previous placement at PIN B10 and honor the location assignment to PIN C14 这个如何解决啊

自己顶一下 跪求大神

就不能多给点信息吗?求助没有诚意,很难得到帮助的。

你用的什么型号的芯片,什么封装的,引脚怎么分配的,要说出来啊。

FPGA是EP4CE22F17,是256管脚的BGA封装的? 不是没有诚意。是我不知道这些信息也需要。小白请谅解~管教的分配就是上面说的,我把一个信号分配给C14,它不让,只让给B10,这两个都是普通IO

感觉从node flag from partition top入手

能说的具体一点吗 谢谢

你这个信号是什么呢?是不是什么特殊信号,或者用了特殊模块,这种情况有可能要分配到特定引脚上。

我并不能分析出问题的具体原因,只是看你的log信息认为这句是问题的关键,这与你的设计相关,我觉得楼上说的有道理。

不是特殊的信号,我就是想加入一个之前没有用到的管脚。

恩 我重新新建了一个工程,重新分配了管脚就好了,谢谢大家。虽然还是不知道具体为啥

回复 管脚分配出现的问题

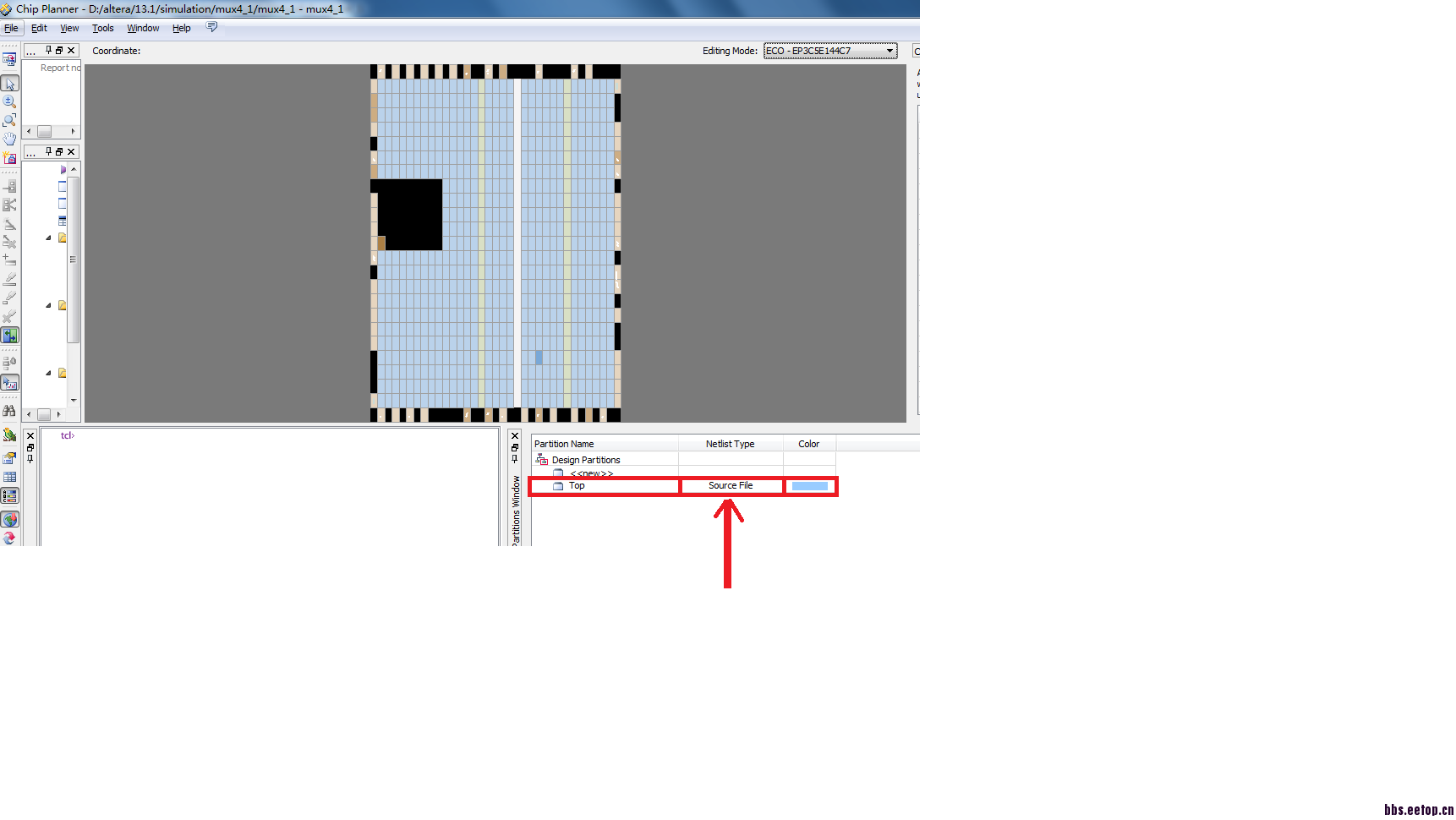

改为红色部分就好了

Do you used design partation function of Quaruts software? If your partation was used post-fitting netlist, it can't change the matche pin assignment.

我也遇到这样的问题,根据你的回复,顺利解决,多谢!