求助,一个简单电路的时序解释,求各位好心人解释下,谢谢!

module div_3(

input clk,

input rst,

output clk_out

);

reg q1;

reg q2;

wire clk1;

wire clk2;

assign clk1=clk^q2;

assign clk2=q1;

always @(posedge clk1 or posedge rst)begin

if(rst)begin

q1<=0;

end

else begin

q1<=~q1;

end

end

always @(posedge clk2 or posedge rst)begin

if(rst)begin

q2<=0;

end

else begin

q2<=~q2;

end

end

assign clk_out=q2;

endmodule

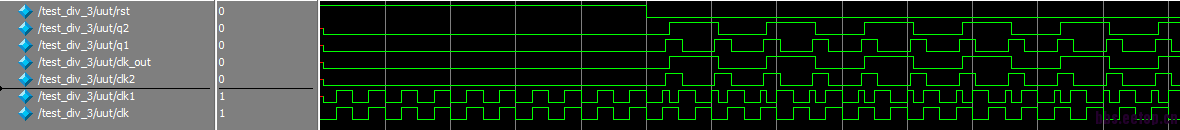

问:为什么clk2,也就是q1的状态好像不单单是在clk1上升沿采样,和clk_out和clk的异或也有关系?但是我在代码中写的就是异或后产生clk1信号,再在clk1的上升沿采样,这个时序不是很懂,求各位好心人解释下。

自顶一下,求助。

没人回答啊,不要沉了

module div15(clkin, clkout, rstn)input clkin;input rstn;output clkout;//自己补充reg ...wire ...always @(posedge clkin or negedge rstn) begin if(!rstn) clk_d2 <= 1'b0; else clk_d2 <= ~clk_d2;endassign clk_neg = ~clkin;assign clkout = clk_neg ^ clk_d2;endmodule

寄存器的赋值加 #1 延迟,然后你再看波形和你想象的有什么不同

不懂,同问

图中,q1的下降沿是在clk1的上升沿完成的,但q1是如何变成高电平的呢

是啊,一直想不明白,q1是怎么变高电平的

和这个有什么关系吗?求详细解答呀

这个语句是可综合的语句吗

哦,找到原因了

这是做ASIC的吗? 没做过。

FPGA上是不能这么做的,你的时钟还与了一下,这都不好,我印象中奇数倍的是上升沿和下降沿做的。

恩,是的,基本上不会用clk来做组合逻辑,我只是想知道那个时序是怎么回事

谢谢啊,我在ise里仿真,怎么clk1的信号没有这个小脉冲

加上小编的#1也没小脉冲吗

你这个代码风格让人蛋疼,写东西总有思想的,不知道你是按怎么个思路写出这么个东西,囧。

最怕的就是clk来自于组合电路

敢这么写的人基本都是很清楚会发生什么才能写。所以你写出来的东西自己应该最清楚才对。

不是我写的,我只是在看它里面的时序,OK?

为什么要这样?

是不是反相器的延迟造成的

总算看懂了。这个要不就是很久以前的代码,要不就是写的人思考了很久。不过还没想出他为什么这么干。感觉有点像逆推的,反正能想到的人很有想法。

5楼说的对!仿真循环时要加延迟的!

复位结束后:

clk clk1 clk2 clkout

0 0 0 0

1 1 1 1

1 0 1 1

0 1 0 1

1 0 0 1

0 1 1 0

0 0 1 0

1 1 0 0

0 0 0 0

學習!學習!

大有收获。

同步执行,,,理解这句话