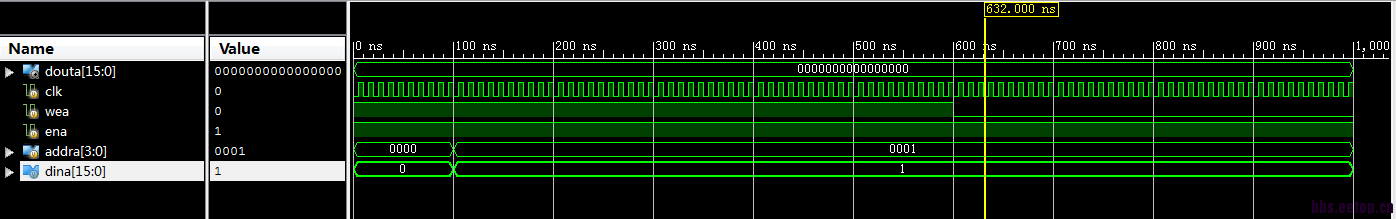

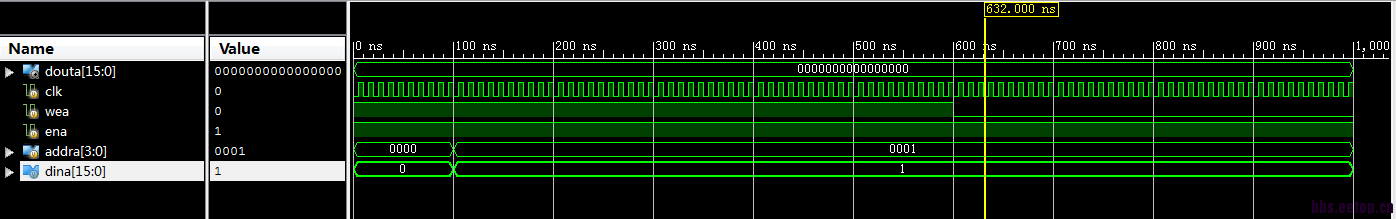

ise 中例化一个single_ram 仿真时多数据为零

时间:10-02

整理:3721RD

点击:

module signel_ram(

input clk,

input wea,

input ena,

input [3:0]addra,

input [15:0] dina,

output [15:0]douta

);

singel_ram_uu your_instance_name (

.clka(clka), // input clka

.ena(ena), // input ena

.wea(wea), // input [0 : 0] wea

.addra(addra), // input [3 : 0] addra

.dina(dina), // input [15 : 0] dina

.douta(douta) // output [15 : 0] douta

);

endmodule

测试文件

module jidfd;

// Inputs

reg clk;

reg wea;

reg ena;

reg [3:0] addra;

reg [15:0] dina;

// Outputs

wire [15:0] douta;

// Instantiate the Unit Under Test (UUT)

signel_ram uut (

.clk(clk),

.wea(wea),

.ena(ena),

.addra(addra),

.dina(dina),

.douta(douta)

);

initial begin

// Initialize Inputs

clk = 0;

wea = 1;

ena = 1;

addra = 0;

dina = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

addra = 1;

dina = 1;

#500;

wea = 0;

end

always #5 clk = ~clk;

//

always@(negedge clk)

//

begin

//

addra = addra + 1;

//

dina = 1;

//

end

endmodule

input clk,

input wea,

input ena,

input [3:0]addra,

input [15:0] dina,

output [15:0]douta

);

singel_ram_uu your_instance_name (

.clka(clka), // input clka

.ena(ena), // input ena

.wea(wea), // input [0 : 0] wea

.addra(addra), // input [3 : 0] addra

.dina(dina), // input [15 : 0] dina

.douta(douta) // output [15 : 0] douta

);

endmodule

测试文件

module jidfd;

// Inputs

reg clk;

reg wea;

reg ena;

reg [3:0] addra;

reg [15:0] dina;

// Outputs

wire [15:0] douta;

// Instantiate the Unit Under Test (UUT)

signel_ram uut (

.clk(clk),

.wea(wea),

.ena(ena),

.addra(addra),

.dina(dina),

.douta(douta)

);

initial begin

// Initialize Inputs

clk = 0;

wea = 1;

ena = 1;

addra = 0;

dina = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

addra = 1;

dina = 1;

#500;

wea = 0;

end

always #5 clk = ~clk;

//

always@(negedge clk)

//

begin

//

addra = addra + 1;

//

dina = 1;

//

end

endmodule

ise 14.1 中 wea 为1 时开始写数据,wea为0时读数据,仿真测试时向1地址写了个数据1,为什么就是读不出数据