求助:关于亚稳态?

如果Q端的输出和输入没有必然关系的话,那样那些所谓的信号同步电路有什么用呢?因为Q端的输出可能就是错的,你在弄几个D触发器打几拍还是错的啊 ? 这样就失去了信号同步电路的意义了。求解 谢谢!

一般来说,如果到CLK2的两个DFF都是0或者都是1,不会使电路发生致命的错误,0或1能否采对是靠协议来保证的。

而同步解决亚稳态,是防止到CLK2上面的DFF是0而到CLK2下面的DFF却是1,这就很可能会导致电路至命的功能错误。打两拍的同步电路就是为了解决这个问题。

有用的 亚稳态有个特点是可以传播。也就是说,如果只打一拍,那么很可能将一个不确定的状态传到logic的下一级。要是打两拍的话,第二拍出现亚稳态的概率将会非常的小,这样就会减少亚稳态的传播。

至于“经过resolution time之后Q端将稳定到0或1上,但是究竟是0还是1,是随机的,与输入没有必然的关系”,举个例子,如果原clk的data由0--->1,在第二拍DFF首次接收第一拍DFF的data的时候,可能接收到0,也可能接收到1.不过都没有关系。如果这时候接收到1,就说明catch到了新的data,如果这时候catch到了0,也没有关系,下一个clock肯定就会catch到1。做跨时钟的时候,就像楼上说的,要靠协议来保障提前或者落后catch新的数据应该OK,不会对logic造成影响.

数据在不同clock domain之间传输,由于相位的不确定性,亚稳态现象存在的概率很大。多级DFF同步处理,也就是把这个概率降到很低,系统可以容忍的限度。这种方法,缺点是数据的不确定性(0 OR 1),如果对准确度要求很高的话,一般采用握手协议(例如:FIFO)

学习了!

出现亚稳态后,第一个周期的第一级DFF的Q是随机的0或1,但是第二个时钟沿之后,第一个DFF的Q就和D一样了。

一般出现亚稳态时都是数据变化阶段,如从0变到1,正常应该采到的数据是1,而第一个DFF因为亚稳态数据变成0,不过没关系,下一个时钟出来的肯定是1,因此不会对最终结果产生影响,只是最终数据延迟了而已

这个应该是协议保证的事情,亚稳态的危害不应该是这个。

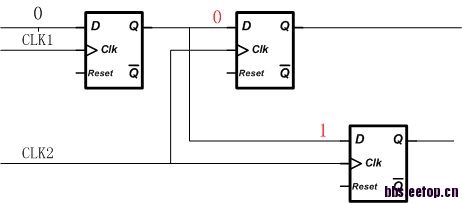

如果CLK1的DFF.Q会接到CLK2.DFF1.D和CLK2.DFF2.D,由于在layout时很难保证CLK1.DFF.Q到CLK2.DFF1.D和CLK2.DFF2.D的走线距离一样长,就可能会出现CLK2.DFF1.D认为是0,而CLK2.DFF2.D认为1,那个电路该如何正常工作呢?

我想上图中应该是演示的会传递亚稳态的设计方式,所以就会出现如你所说的无法正常工作。一般会在把数据送给下级用之前,用至少2级寄存器同步一下,得到稳定的值(且不管当前值是不是对的),这样就不会出现下游的2个不同的寄存器采样得到不一样的值了。

谢谢各位大侠的指导,7楼的指导很给力 谢谢!

我也跟着学习了。

路过学习……也困惑这个……如果出错了,是不是也被算在了MTBF里面?

恩,同意观点

我认为,你应该先让这个q信号经过两个串联的寄存器后,在分散到自己时钟域的寄存器上。这样就不会出现不确定了。

学些了

单bit传输一般是打两拍,如果是单bit控制线和多bit数据,那就要建立握手协议;最复杂的是异步FIFO