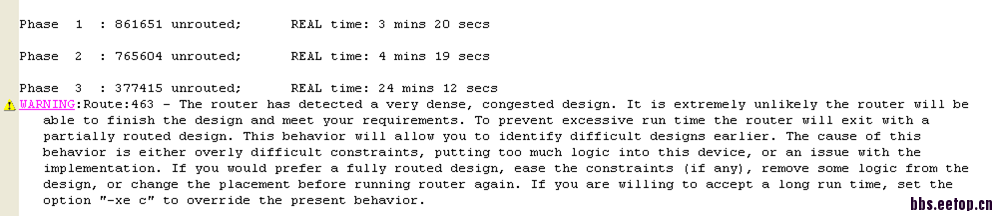

布局布线的时候遇到congestion的问题无法通过

时间:10-02

整理:3721RD

点击:

verilo代码如下:

flow_ctrl_in_op_beforedly={

flow_ctrl_out_ip[ Matrix_N[node] ][flow_ctrl_width*1:flow_ctrl_width*2-1],

flow_ctrl_out_ip[ Matrix_S[node] ][flow_ctrl_width*0:flow_ctrl_width*1-1],

flow_ctrl_out_ip[ Matrix_E[node] ][flow_ctrl_width*3:flow_ctrl_width*4-1],

flow_ctrl_out_ip[ Matrix_W[node] ][flow_ctrl_width*2:flow_ctrl_width*3-1],

};

主要是这一段代码,原先寄存器Matrix_N,Matrix_S,Matrix_E,Matrix_W为定值的时候可以顺利通过,将寄存器设置为外部配置之后就出现了这个问题,提示过于拥塞,node为0-15,flow_ctrl_width为64。尝试了很多方法,比如在布局布线的时候忽略时序的问题,结果就会导致无限制的布局布线下去,几天都跑不出来结果,现在基本上已经把所有的时序约束去掉了。在官网上查找类似的问题只提示了说可以设置两个环境变量,但是还是没有什么效果。

从设计的角度上来讲,我只是设计一个可以全配置的交叉矩阵,对16个节点的信号(位宽64)进行交叉选通,关于简化这个设计,不知还有什么高见。毕业设计内容,恳请出谋划策。