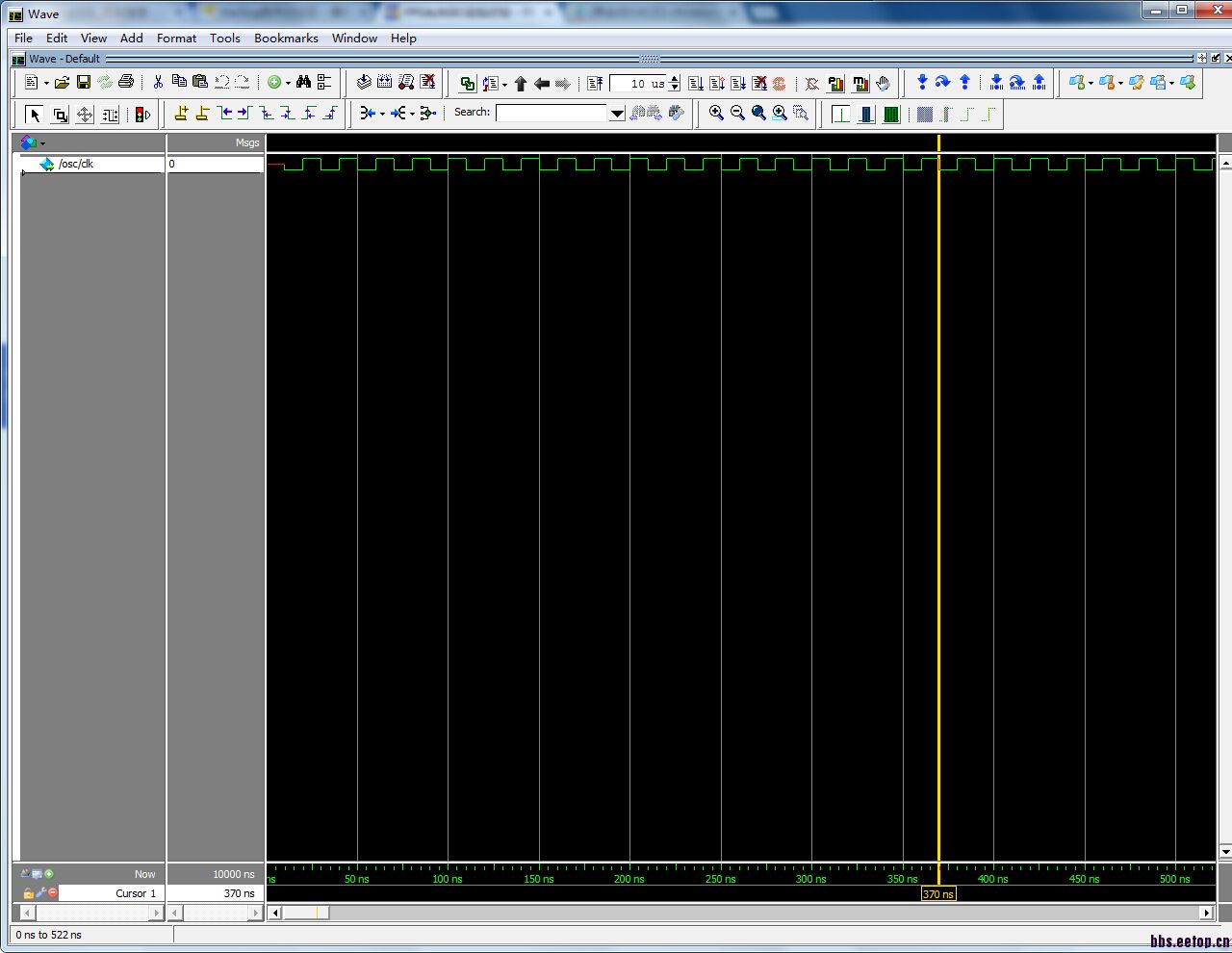

verilog阻塞赋值问题

output clk;

reg clk;

initial #10 clk = 0;

always @(posedge clk,negedge clk)

begin

#10 clk <= ~clk;

end

endmodule以上代码中,always后面的敏感信号列表采用的是边沿触发方式。但是initial中使用阻塞赋值,照理来说当赋值结束后clk一直处于低电平状态,应该不会触发always的啊。但是实际上仿真结果却显示已经触发了。

本人初学verilog,有些地方不太明白,还望各位指点一二。

自己顶一下!

你不是posedge和negedge都放进@了吗?

bangd

但是initial中使用阻塞赋值,照理来说当赋值结束后clk一直处于低电平状态,应该不会触发always的啊。

?

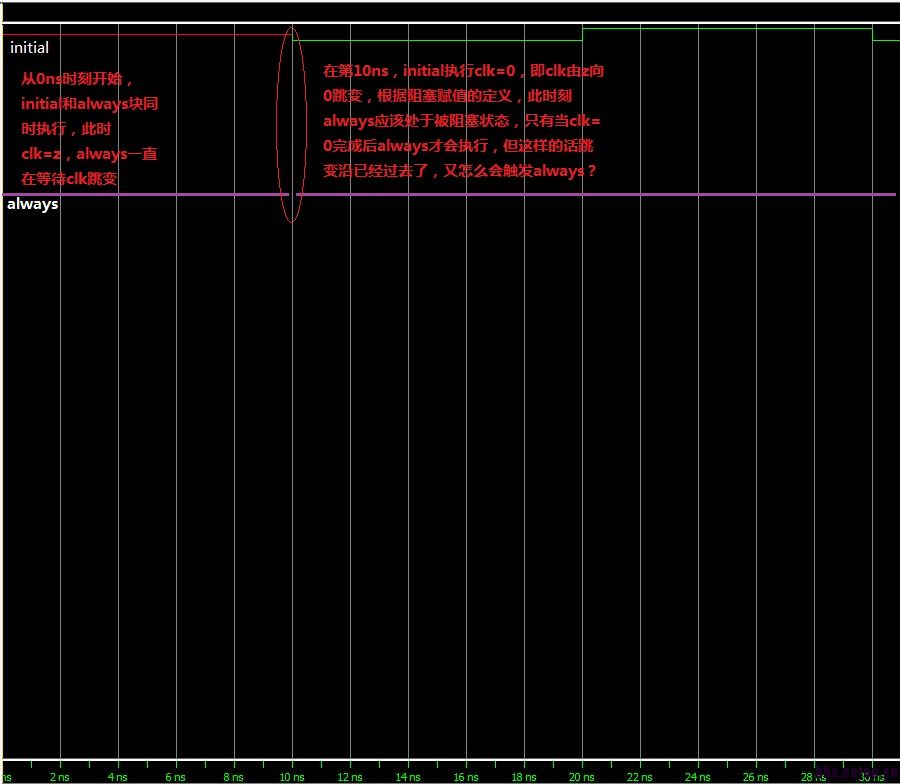

我的理解:

#0时刻加载clk = 0;

#10时刻执行clk = 0;并触发always模块,加载clk <= ~clk;

#20时刻执行clk <= ~clk;并可再次触发always模块,加载clk <= ~clk;

...

...

如果你将clk<=~clk改为clk = ~clk,那又不一样了!

任何reg型数据的初始值是z啊,你看波形clk一开始有一小段z的。

initial以后才变成0,z->0的变化属于下降沿。

initial只会运行一次吧?

我的意思是,

是的,只运行一次

#10时刻执行clk = 0;执行的是阻塞赋值,为什么还会触发always模块呢?要是这样的话,阻塞和非阻塞还有什么区别?

我感觉阻塞赋值不是这么理解的。

阻塞赋值只对同一个begin end块内有阻塞效果,例如

a=b;

c=a;

那么肯定会等a=b完成了再执行c=a

不同的inial、always块是并行执行的,不会阻塞

结果没有错,理解好并行还有初始化

8楼是对的

reg默认初始值应该是x吧。

这。我竟然无言语对!不知道你的仿真激励文件是怎么写的。

触发Always模块的是事件!

自己驱动自己。

Do you understand what is the blocking and none-blocking assignment?

none-blocking example: That is the register element.

always @(posedge CLK or negedge RESETN)

if(~RESETN)

A <= 1'b0;

else

A <= B;

blocking assignment: That is the combination circuit

always @*

if(~RESETN)

A = 1'b0;

else if(signal_c | singal_d)

A = B;

看到这么写,有点蛋疼。

A: initial #10 clk = 0;

B: always @(posedge clk,negedge clk)

C: begin

D: #10 clk <= ~clk;

E: end

第一个always触发发生在A:initial 里面clk有z->0的时刻,第二个always触发发生第一个always触发的时刻,一次类图,后一个always中clk的变化总是下一个always触发的条件。

嗯,知道了。初学verilog,确实不太明白阻塞和非阻塞。谢谢你。ps:貌似他们都没搞清楚我在问什么...

没有仿真激励文件,这个模块都没有输入的。这就是夏宇闻老师 verilog数字系统设计教程 上的一个例题,我当时只是不明白阻塞和非阻塞究竟只是对本块阻塞还是对所有的并行块都阻塞,现在已经明白了,谢谢你的耐心解答。

很简单的问题,居然没有看到一个正确答案。算了,我懒得说。

我理解阻塞式赋值是顺序执行;非阻塞赋值是并行执行。

阻塞赋值只对同一个begin end块内有阻塞效果。

clk信号初始值为z,10个时间单位时变为0,z到0被认定为一个触发沿,这个触发沿触发了#10 clk <= ~clk 语句,也就是说再过10个时间单位,clk由0变为1,这次clk的转变又形成一个上升沿,将再次触发#10 clk <= ~clk 语句,再过10个时间单位后,clk由1变为0,如此循环往复……

这个case中,clk信号的跃变自为因果