Verilog 赋值的问题

时间:10-02

整理:3721RD

点击:

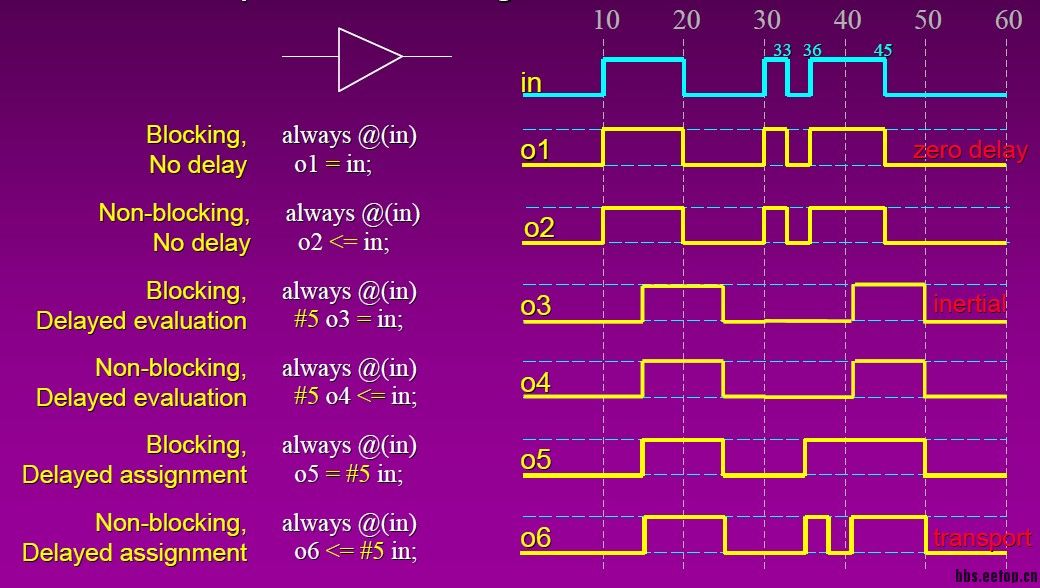

请问O5与O6波形为啥有区别?

求高手解答

in 的窄脉冲宽3ns。 o5 = #5 in 是阻塞赋值,也就是说它执行完后(5ns后)才往下执行(o5为高)。但是它执行后,in窄脉冲的下降沿就不能感知到了,下一个always @(in)感知到的是宽脉冲的上升沿,所以o5仍然为高。

o6就不用解释了吧。

那就是说 o5 = #5 in 会导致always块在这5ns中都不会再被触发

而o5 <= #5 in 能立刻执行完毕,使always块能够被33ns的下降沿触发

为啥阻塞赋值会导致always不再触发,而非阻塞则没有这个问题?

还是不太能理解这个现象,能不能跟我说说这个问题的名字是什么,我自己去查资料吧。

谢谢!

延迟赋值相关问题,延迟阻塞赋值问题,......。其它合适的名字,都行。

只是我个人的理解,仅供参考。

谢谢!