大家好,推荐一段乘法合并的写法,但是有问题,求助!

时间:10-02

整理:3721RD

点击:

为了节省DSP slice资源,将两个乘法合到一个乘法器中进行运算,代码如下:

module Mix_i_q(

input clk,

input [3:0] signal_if,

input [4:0] sin,

input [4:0] cos,

output [7:0] mix_idata,

output [7:0] mix_qdata

);

wire [14:0] mult_a;

wire [14:0] mult_b;

wire [29:0] mult_p;

assign mult_a={{{signal_if[3],signal_if}+{5{cos[4]}}},{5{cos[4]}},cos};

assign mult_b={{sin+{5{signal_if[3]}}},{6{signal_if[3]}},signal_if};

assign mix_idata=mult_p[27:20];

assign mix_qdata=mult_p[7:0];

mult_15_x_15 u0

(

.clk (clk),

.a (mult_a),

.b (mult_b),

.p (mult_p)

);

endmodule

原理很简单,在这里就相当于是:

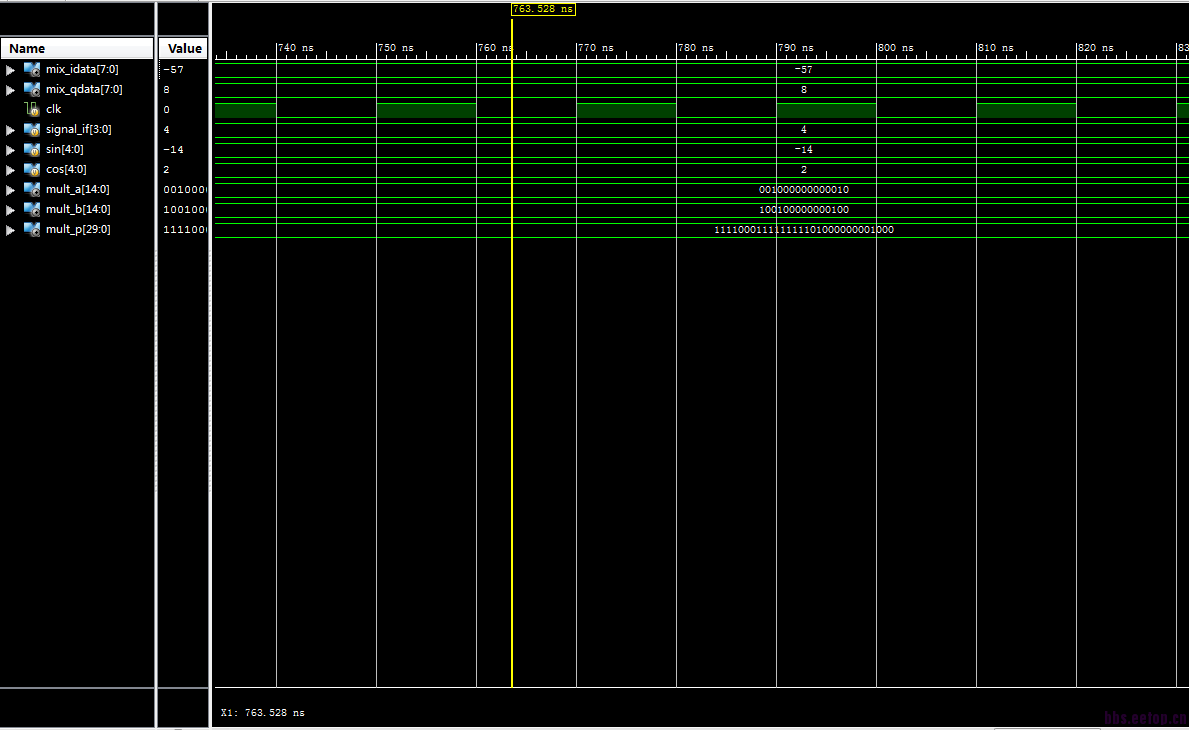

(a*2^10+b)乘以(c*2^10+d),取低位的bd值和20位以上的ac值,感觉是没有任何问题的,但是实际仿真时发现,如果a、b、c、d都是正数时,运算结果正确,但是有一个乘数为负数(补码形式),运算结果中高位结果少1,即结果为ac-1。

如图所示,求论坛大神破我疑团。

有没有论坛大神前来相助啊?

建议把乘法器扩展到16位,同时对输入做一位的符号扩展

楼上正解!

不行啊,我试过了,还是小1。请问这种改法的依据是什么呢?或者说我错在哪了?

请问这个依据是什么?我改了之后还是不对啊,而且我感觉位宽足够啊!

强顶不要沉,继续求助!

我觉得LZ应该设计的复杂了。应该还有很简单易行的方案

你期望的等式是:(a*2^10+b)*(c*2^10+d) 》20 = a*c

当结果为负数 ,等式取反加一后的右移结果,和等式直接右移后再取反加一的结果是有差别的。